Support Information

M9328MX21ADSE User’s Manual, Rev. A

Freescale Semiconductor 3-5

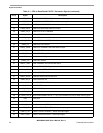

66 UART1_TXD UART1 TRANSMITTED DATA — Serial output signal

67 UART2_RTS UART2 REQUEST TO SEND — Active low input signal

68 UART2_CTS UART2 CLEAR TO SEND — Active low output signal

69 UART2_RXD UART2 RECEIVED DATA — Serial input signal

70 UART2_TXD UART2 TRANSMITTED DATA — Serial output signal

71 BOOT3 BOOT location select input bit 3

72 BOOT2 BOOT location select input bit 2

73 BOOT1 BOOT location select input bit 1

74 BOOT0 BOOT location select input bit 0

75 PWM0 PULSE WIDTH MODULATOR OUTPUT

76 TIN TIMER INPUT CAPTURE — Timer input

77 JTAG_CTRL JTAG CONTROL — input to select between and ARM and normal JTAG operation

78 TOUT TIMER OUTPUT

79 RESET_IN_B RESET IN — Active low reset signal to the processor

80 RESET_OUT_B RESET OUT — Active low reset signal from the processor

81 POR_B POWER ON RESET

82 RTCK_GPIO RETURN CLOCK — JTAG signal, can be general purpose I/O

83 CLKMODE0 CLOCK MODE BIT 0 — Selects PLL bypass modes

84 CLKMODE1 CLOCK MODE BIT 1 — Selects PLL bypass modes

85 B_CS5_B BUFFERED CHIP SELECTS 5 — Chip select signal, active low output (Reserved)

86 B_CS4_B BUFFERED CHIP SELECTS 4 — Chip select signal, active low output (Reserved)

87 B_CS1_B BUFFERED CHIP SELECTS 1 — Chip select signal, active low output

88 B_CS0_B BUFFERED CHIP SELECTS 0 — Chip select signal, active low output (Reserved)

89 B_OE_B

BUFFERED OUTPUT ENABLE— Enables external devices to drive the data bus,

active low output

90 B_RW_B

BUFFERED READ/WRITE — A low indicates an external write operation, a high indicates

a read operation type

91 B_NEXUSEVTI Internal use only

92 NEXUS_EN_B Internal use only

93 B_A0 BUFFERED ADDRESS 0— Buffered address output (Reserved)

94 B_A1 BUFFERED ADDRESS 1— Buffered address output

95 B_A2 BUFFERED ADDRESS 2 — Buffered address output

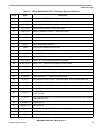

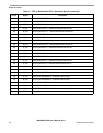

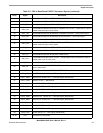

Table 3-1. CPU to Base Board PX1/PY1 Connector Signals (continued)

Pin(s) Signal Description