Si53xx-RM

Rev. 0.5 121

APPENDIX B—FREQUENCY PLANS AND JITTER PERFORMANCE (Si5316, Si5319,

Si5323, S

I5324, Si5326, Si5327, Si5366, Si5368, Si5369, Si5374, Si5375)

Introduction

To achieve the best jitter performance from Narrowband Any-Frequency Clock devices, a few general guidelines

should be observed:

High f3 Value

f3 is defined as the comparison frequency at the Phase Detector. It is equal to the input frequency divided by N3.

DSPLLsim automatically picks the frequency plan that has the highest possible f3 value and it reports f3 for every

new frequency plan that it generates. f3 has a range from 2 kHz minimum up to 2 MHz maximum. The two main

causes of a low f3 are a low clock input frequency (which establishes an upper bound on f3) and a PLL multiplier

ratio that is comprised of large and mutually prime nominators and denominators. Specifically, for

CKOUT = CKIN x (P/Q), if P and Q are mutually prime and large in size, then f3 may have a low value. Very low

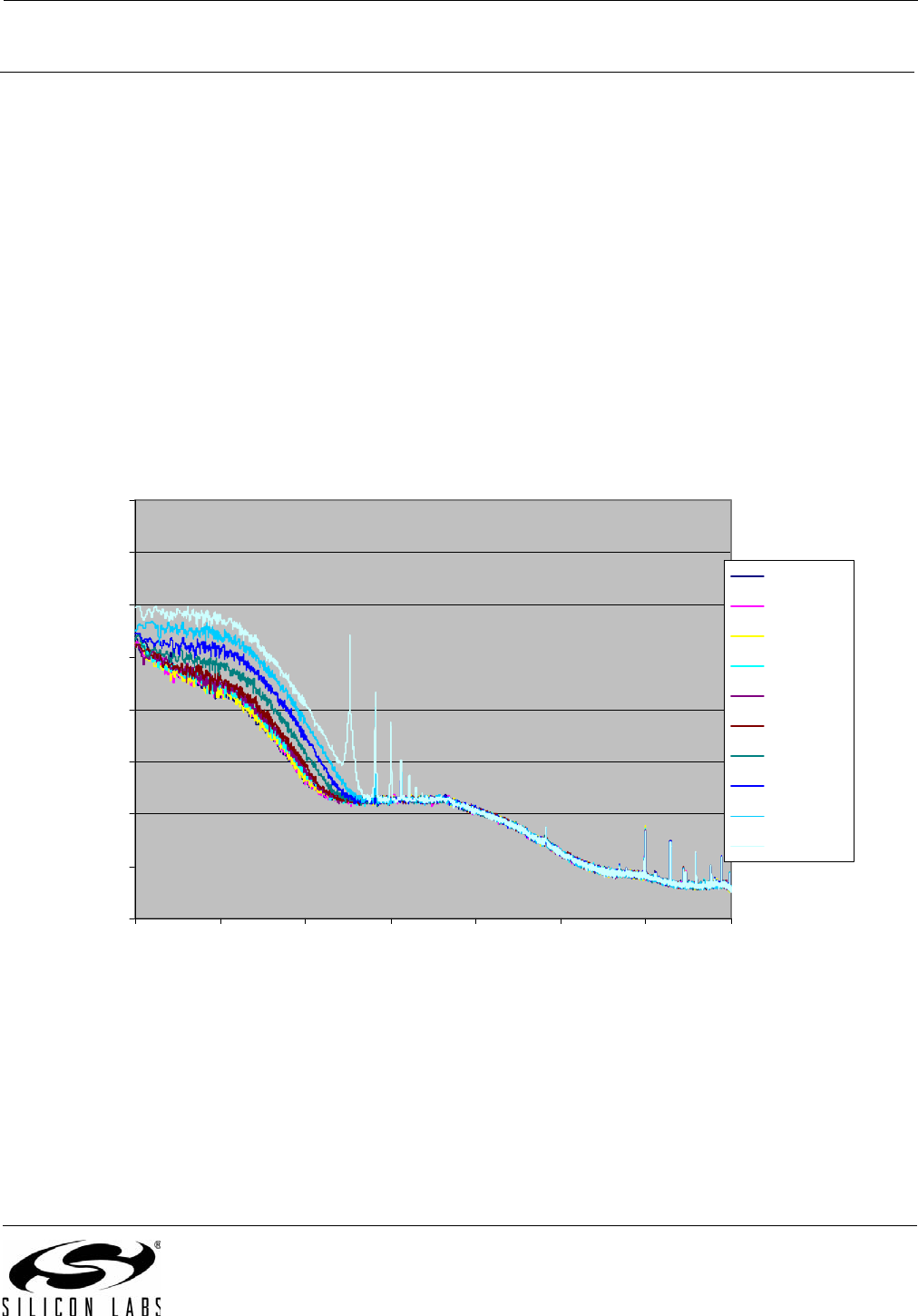

values of f3 usually result in extra jitter as can be seen in Figure 60.

Figure 60. Jitter vs. f3

For the f3 study, the input, output and DCO frequencies were held constant while the dividers were manipulated by

hand to artificially reduce the value of f3. Two effects can be seen as f3 approaches the 2 kHz lower limit: there are

“spur like” spikes in the mid-band and the noise floor is elevated at the near end. It is also clear that once f3 is

above roughly 50 kHz, there is very little benefit from further increasing f3. Note that the loop bandwidth for this

study was 60 Hz and any noise below 60 Hz is a result of the input clock, not the Any-Frequency Precision Clock.

Phase Noise versus f3, 155.52 MHz in, 622.08 MHz out

-160

-140

-120

-100

-80

-60

-40

-20

0

10 100 1000 10000 100000 1000000 1E+07 1E+08

Frequency (Hz)

Phase Noise (dBc/Hz)

1709 kHz

855 kHz

427 kHz

214 kHz

107 kHz

54 kHz

27 kHz

13 kHz

7 kHz

3 kHz