Si53xx-RM

40 Rev. 0.5

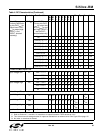

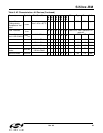

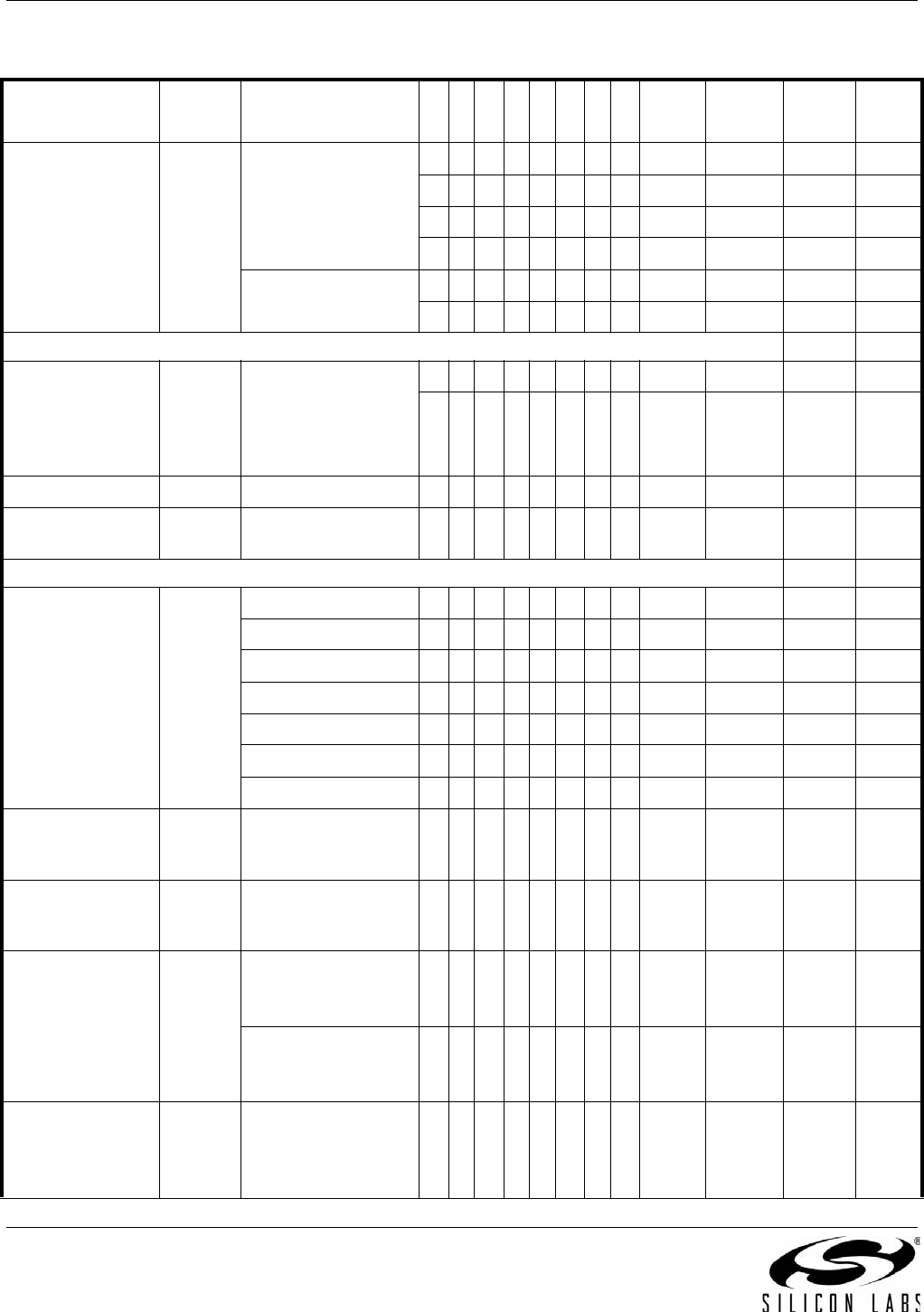

Table 8. AC Characteristics—All Devices

Parameter

Symbol Test Condition

Si5316

Si5322

Si5324

Si5325

Si5365

Si5366

Si5367

Si5368

Min Typ Max Units

Input Frequency

CKN

F

19.38 — 710 MHz

19.43 — 707.35 MHz

0.002 — 707.35 MHz

10 — 710 MHz

When used as frame

synchronization input

—0.008 —MHz

2—512kHz

CKIN_n Input Pins

Input Duty Cycle

(Minimum Pulse

Width) CKN

DC

Whichever is smaller

(i.e., the 40% / 60 %

limitation applies only

to high frequency

clocks)

40 — 60 %

2——ns

Input Capacitance CKN

CIN

—— 3pF

Input Rise/Fall

Time

CKN

TRF

20–80%

See Figure 17

—— 11ns

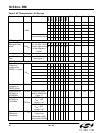

CKOUT_n Output Pins (See individual data sheets for speed grade limits)

Output Frequency

(Output not

configured for

CMOS or tri-state)

CK

OF

19.38 — 710 MHz

19.43 — 1049 MHz

0.008 — 1049 MHz

10 — 945 MHz

0.002 — 945 MHz

970 — 1134 MHz

1.213 — 1.4 GHz

Maximum Output

Frequency in

CMOS Format

CKO

FMC

— — 212.5 MHz

Output Rise/Fall

(20–80%) at

622.08 MHz

CKO

TRF

Output not config-

ured for CMOS See

Figure 17

— 230 350 ps

Output Rise/Fall

(20–80%) at

212.5 MHz

CKO

TRF

CMOS Output

V

DD

= 1.62

Cload = 5 pF

—— 8ns

CMOS Output

V

DD

= 2.97

Cload = 5 pF

—— 2ns

Output Duty Cycle

Differential

Uncertainty

CKO

DC

100 Load

Line to Line

Measured at 50%

Point (not for CMOS)

——±40ps