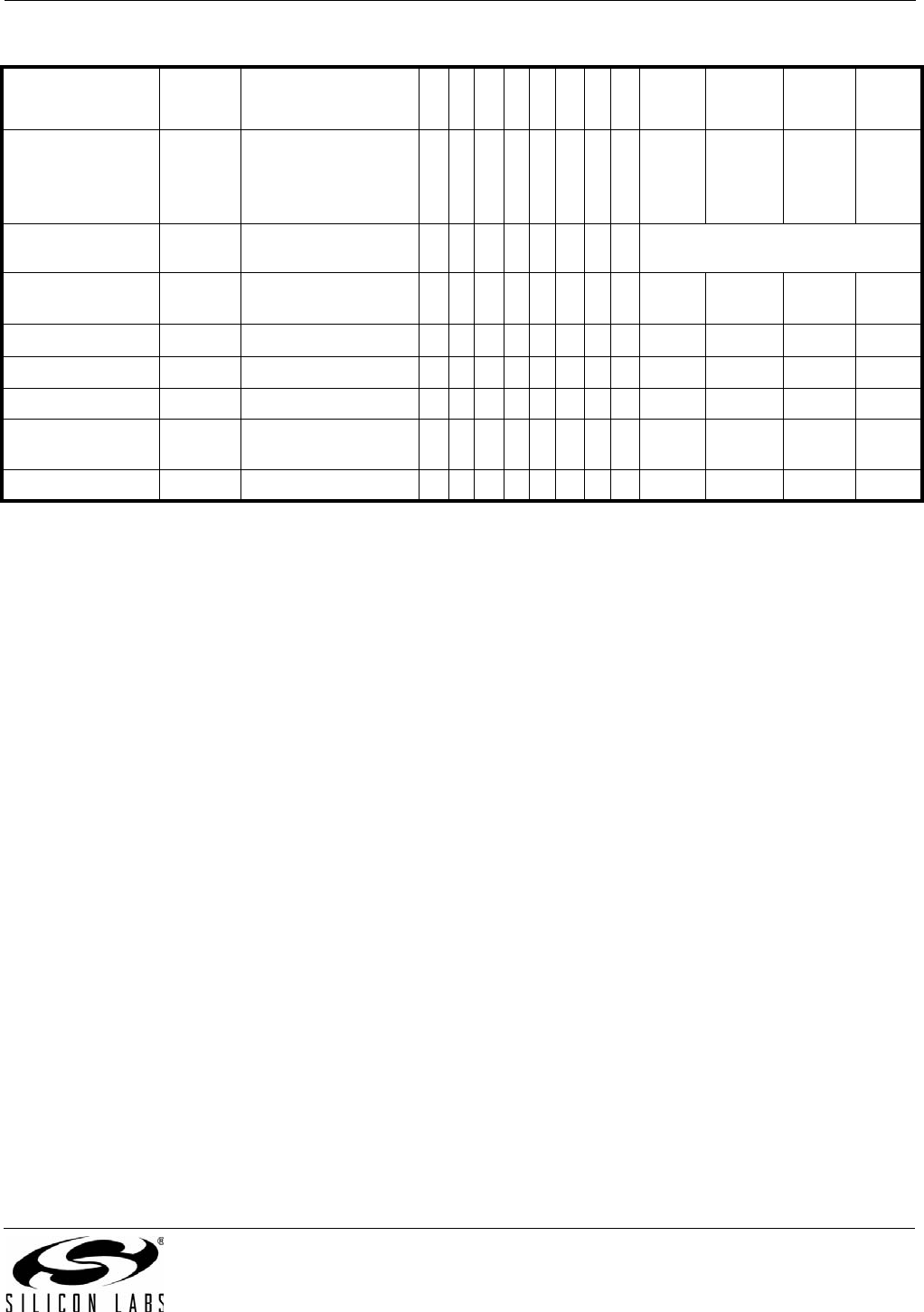

Si53xx-RM

Rev. 0.5 43

Output Phase

Change due to

Temperature Vari-

ation

t

TEMP

Max phase changes

from –40 to +85 °C

— 300 500 ps

Jitter Tolerance

J

TOL

See "5.2.3. Jitter Tolerance" on

page 49.

Phase Noise

fout = 622.08 MHz

CKO

PN

1 kHz Offset

— –106 –87 dBc/Hz

10 kHz Offset

— –121 –100 dBc/Hz

100 kHz Offset

—–132–110dBc/Hz

1 MHz Offset

— –132 –125 dBc/Hz

Subharmonic

Noise

SP

SUBH

Phase Noise @

100 kHz Offset

— –88 –76 dBc

Spurious Noise

SP

SPUR

— –93 –70 dBc

Table 8. AC Characteristics—All Devices (Continued)

Parameter

Symbol Test Condition

Si5316

Si5322

Si5324

Si5325

Si5365

Si5366

Si5367

Si5368

Min Typ Max Units