Si53xx-RM

Rev. 0.5 87

7.6. Digital Hold

All Any-Frequency Precision Clock devices feature a holdover mode, whereby the DSPLL is locked to a digital

value.

7.6.1. Narrowband Digital Hold (Si5316, Si5324, Si5326, Si5368, Si5369, Si5374)

After the part's initial self-calibration (ICAL), when no valid input clock is available, the device enters digital hold.

Referring to the logical diagram in "Appendix D—Alarm Structure" on page 144, lack of clock availability is defined

by following the boolean equation for the Si5324, Si5326, and Si5374:

(LOS1_INT OR FOS1_INT) AND (LOS2_INT OR FOS2_INT) = enter digital hold

The equivalent Boolean equation for the Si5327 is as follows:

LOS1 and LOS2 = enter digital hold

The equivalent boolean equation for the Si5367, Si5368, and Si5369 is as follows:

(LOS1_INT OR FOS1_INT) AND (LOS2_INT OR FOS2_INT) AND

(LOS3_INT OR FOS3_INT) AND (LOS4_INT OR FOS4_INT) = enter digital hold

7.6.1.1. Digital Hold Detailed Description (Si5324, Si5326, Si5327, Si5368, Si5369, Si5374)

In this mode, the device provides a stable output frequency until the input clock returns and is validated. Upon

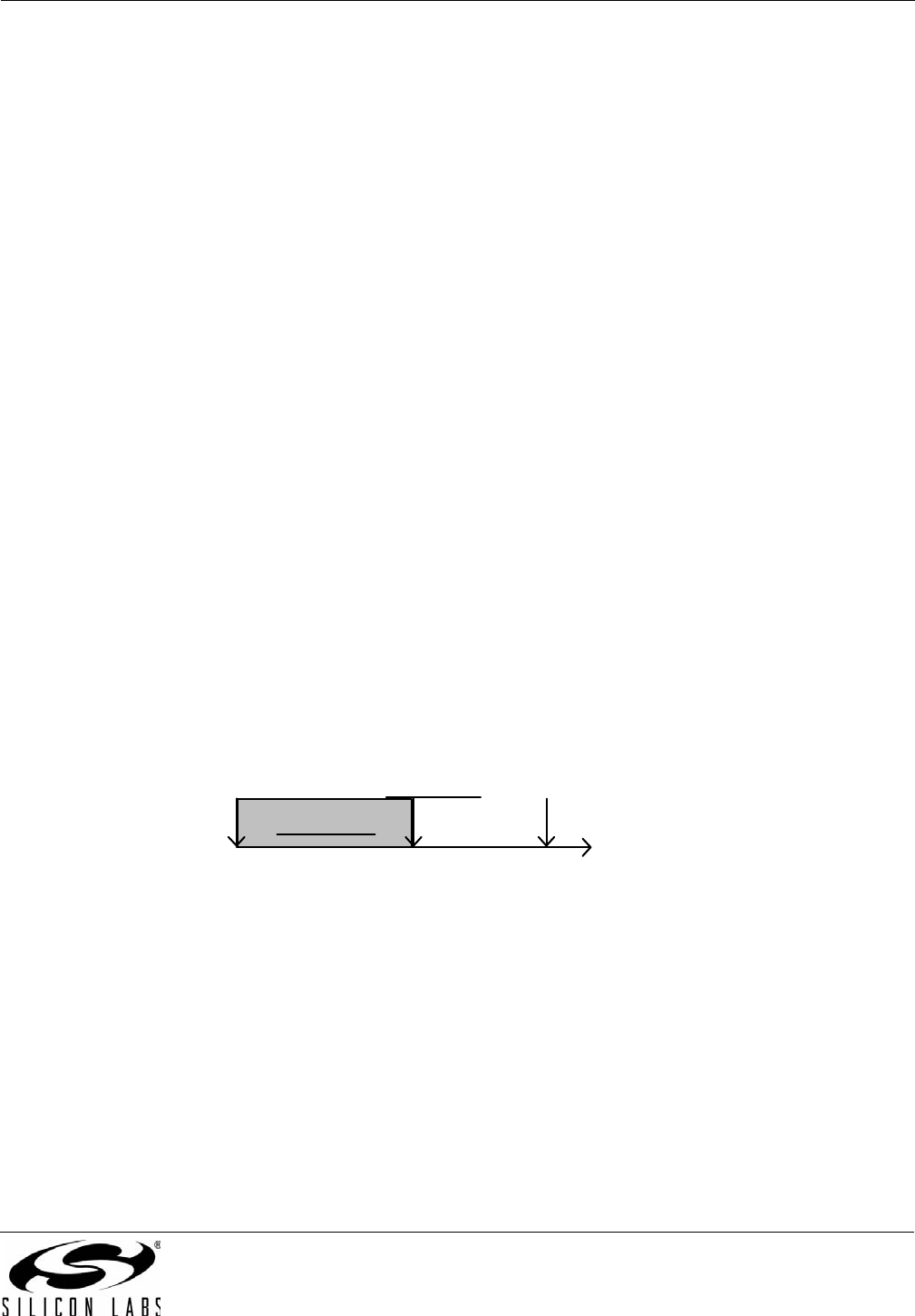

entering digital hold, the internal DCO is initially held to its last frequency value, M (See Figure 30). Next, the DCO

slowly transitions to a historical average frequency value supplied to the DSPLL, M

HIST

, as shown in Figure 30.

Values of M starting from time t = –(HIST_DEL + HIST_AVG) and ending at t = –HIST_DEL are averaged to

compute M

HIST

. This historical average frequency value is taken from an internal memory location that keeps a

record of previous M values supplied to the DCO. By using a historical average frequency, input clock phase and

frequency transients that may occur immediately preceding digital hold do not affect the digital hold frequency.

Also, noise related to input clock jitter or internal PLL jitter is minimized.

Figure 30. Parameters in History Value of M

The history delay can be set via the HIST_DEL[4:0] register bits as shown in Table 42 and the history averaging

time can be set via the HIST_AVG[4:0] register bits as shown in Table 43. The DIGHOLDVALID register can be

used to determine if the information in HIST_AVG is valid and the device can enter SONET/SDH compliant digital

hold. If DIGHOLDVALID is not active, the part will enter VCO freeze instead of digital hold.

Time

Digital Hold

@

t = 0

MM

HIST

t = –HIST_DEL

HIST_AVG