Si53xx-RM

Rev. 0.5 57

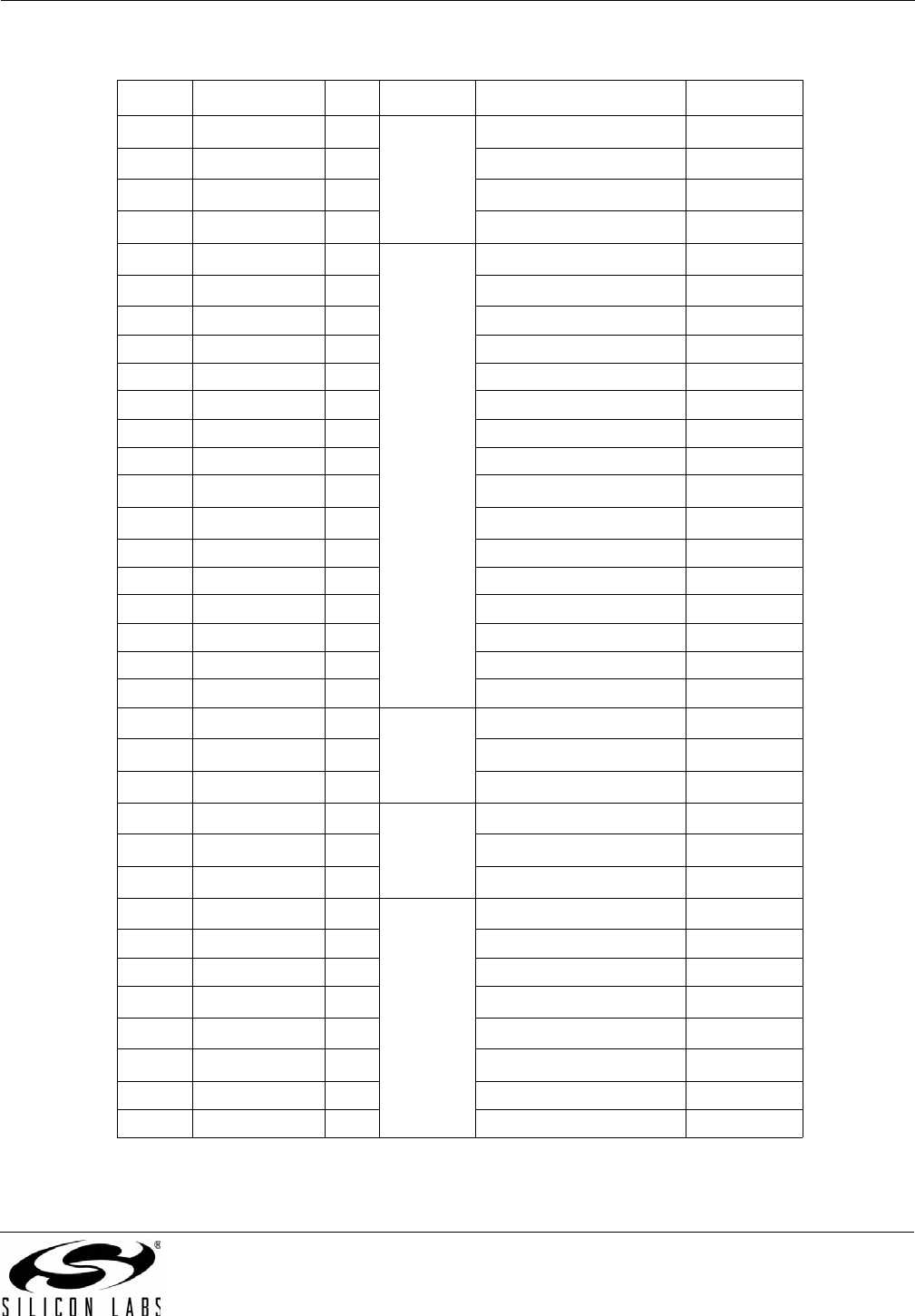

Table 17. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0)

Setting FRQSEL[3:0]

WB

f

IN

(MHz) Mult Factor f

OUT

* (MHz)

0LLLL

15.625 2 31.25

1LLLM

462.5

2 LLLH

8125

3LLML

16 250

4LLMM

25 17/4 106.25

5 LLMH

5125

6 LLHL 25/4 x 66/64 161.13

7 LLHM 51/8 x 66/64 164.36

8 LLHH 25/4 x 66/64 x 255/238 172.64

9 LMLL 25/4 x 66/64 x 255/237 173.37

10 LMLM 51/8 x 66/64 x 255/238 176.1

11 LMLH 51/8 x 66/64 x 255/237 176.84

12 LMML

17/2 212.5

13 LMMM

17 425

14 LMMH 25 x 66/64 644.53

15 LMHL 51/2 x 66/64 657.42

16 LMHM 25 x 66/64 x 255/238 690.57

17 LMHH 25 x 66/64 x 255/237 693.48

18 LHLL 51/2 x 66/64 x 255/238 704.38

19 LHLM 51/2 x 66/64 x 255/237 707.35

20 LHLH

31.25 2 62.5

21 LHML

4125

22 LHMM

8250

23 LHMH

53.125 2 106.25

24 LHHL

4212.5

25 LHHM

8425

26 LHHH

106.25 3/2 x 66/64 164.36

27 MLLL 3/2 x 66/64 x 255/238 176.1

28 MLLM 3/2 x 66/64 x 255/237 176.84

29 MLLH

2212.5

30 MLML

4425

31 MLMM

6x66/64 657.42

32 MLMH 6 x 66/64 x 255/238 704.38

33 MLHL 6 x 66/64 x 255/237 707.35