t

RC

(m)

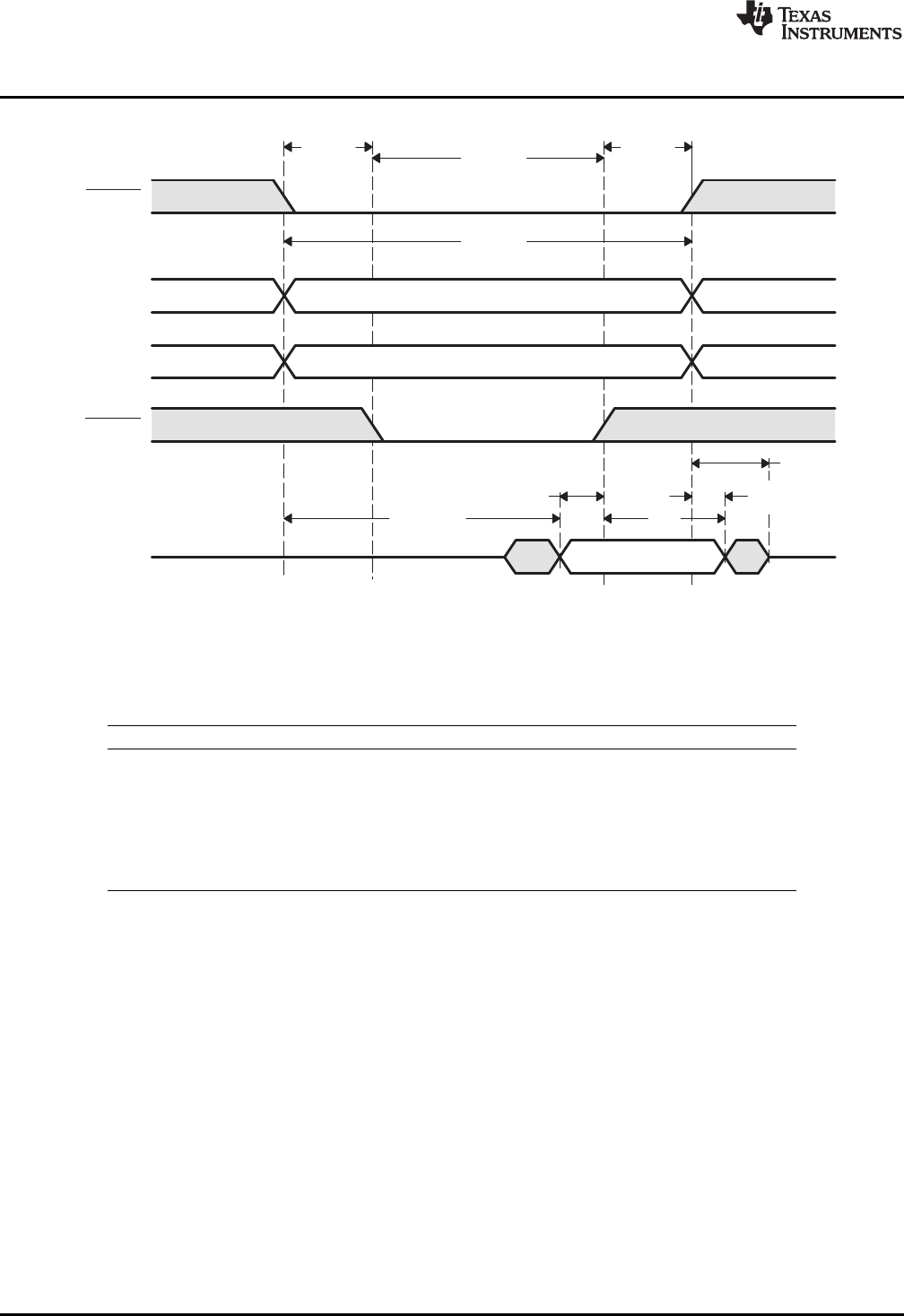

Strobe

Setup Hold

EM_CS

EM_A[21:0]

EM_BA[1:0]

EM_OE

EM_D[15:0]

t

ACC

(m)

t

SU

t

H

t

COD

(m)

t

OH

(m)

Use Cases

www.ti.com

Figure 12. Timing Waveform of an ASRAM Read

For a write access, Table 18 lists the AC timing specifications that must be satisfied.

Table 18. ASRAM Input Timing Requirements for a Write

Parameter Description

t

WP

Write Pulse width

t

AW

Address valid to end of Write

t

DS

Data Setup time

t

WR

Write Recovery time

t

DH

Data Hold time

t

WC

Write Cycle time

32

Asynchronous External Memory Interface (EMIF) SPRUEQ7C–February 2010

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated