www.ti.com

Registers

4.9 NAND Flash Status Register (NANDFSR)

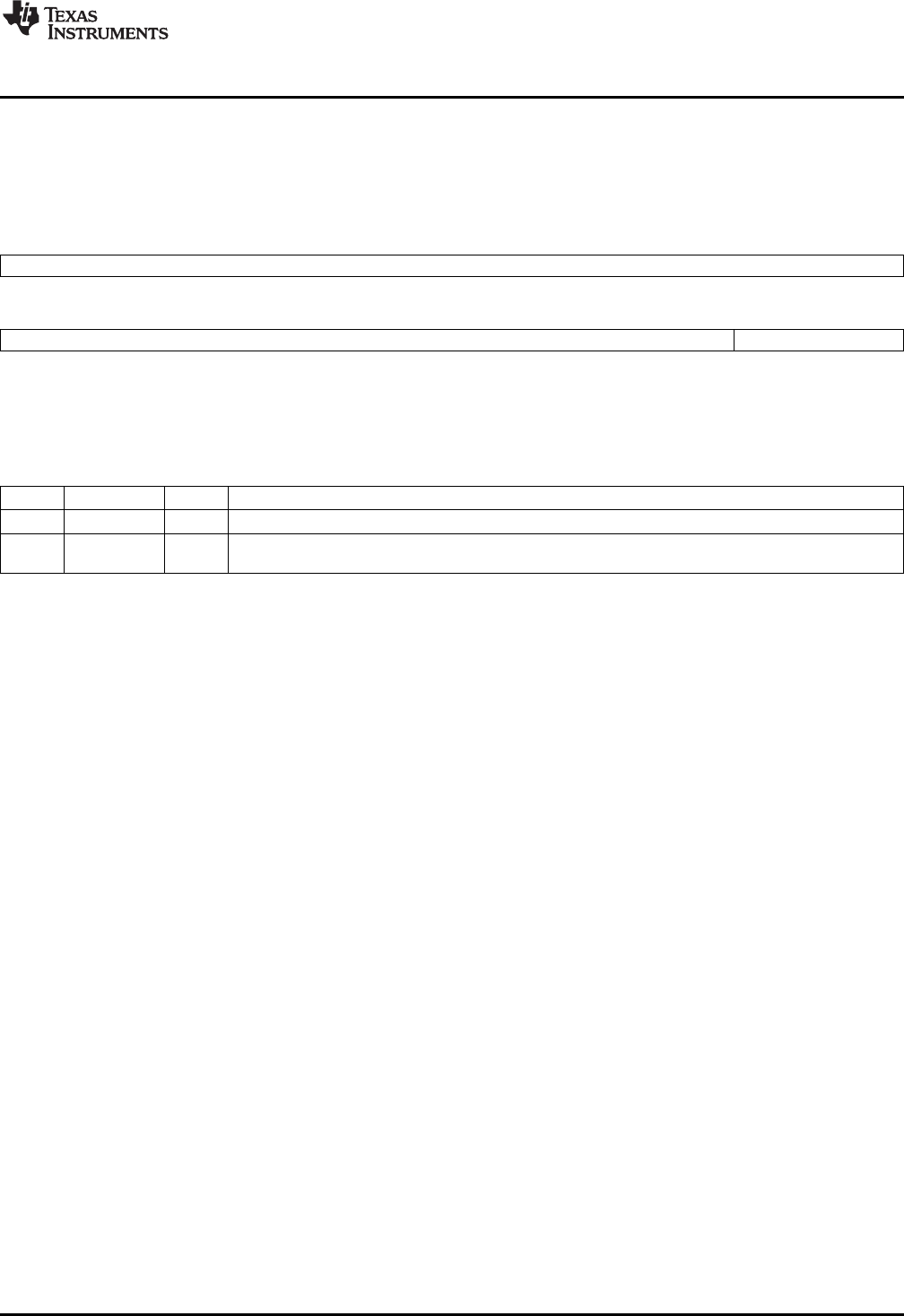

The NAND Flash status register (NANDFSR) is shown in Figure 28 and described in Table 41.

Figure 28. NAND Flash Status Register (NANDFSR)

31 16

Reserved

R-0

15 4 3 0

Reserved WAITST

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 41. NAND Flash Status Register (NANDFSR) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved

3-0 WAITST 0-Fh Raw status of the EM_WAITn input pin. The WPn bit in the asynchronous wait cycle configuration

register (AWCCR) has no effect on WAITST.

4.10 NAND Flash n ECC Registers (NANDF1ECC-NANDF4ECC)

The NAND Flash n ECC register (NANDECCn) is shown in Figure 29 and described in Table 42. For 8-bit

NAND Flash, P1O, P2O, and P4O bits are column parities; P8O to P2048O bits are row parities. For

16-bit NAND Flash, P1O, P2O, P4O, and P8O bits are column parities; P16O to P2048O bits are row

parities.

61

SPRUEQ7C–February 2010 Asynchronous External Memory Interface (EMIF)

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated