Registers

www.ti.com

4.8 NAND Flash Control Register (NANDFCR)

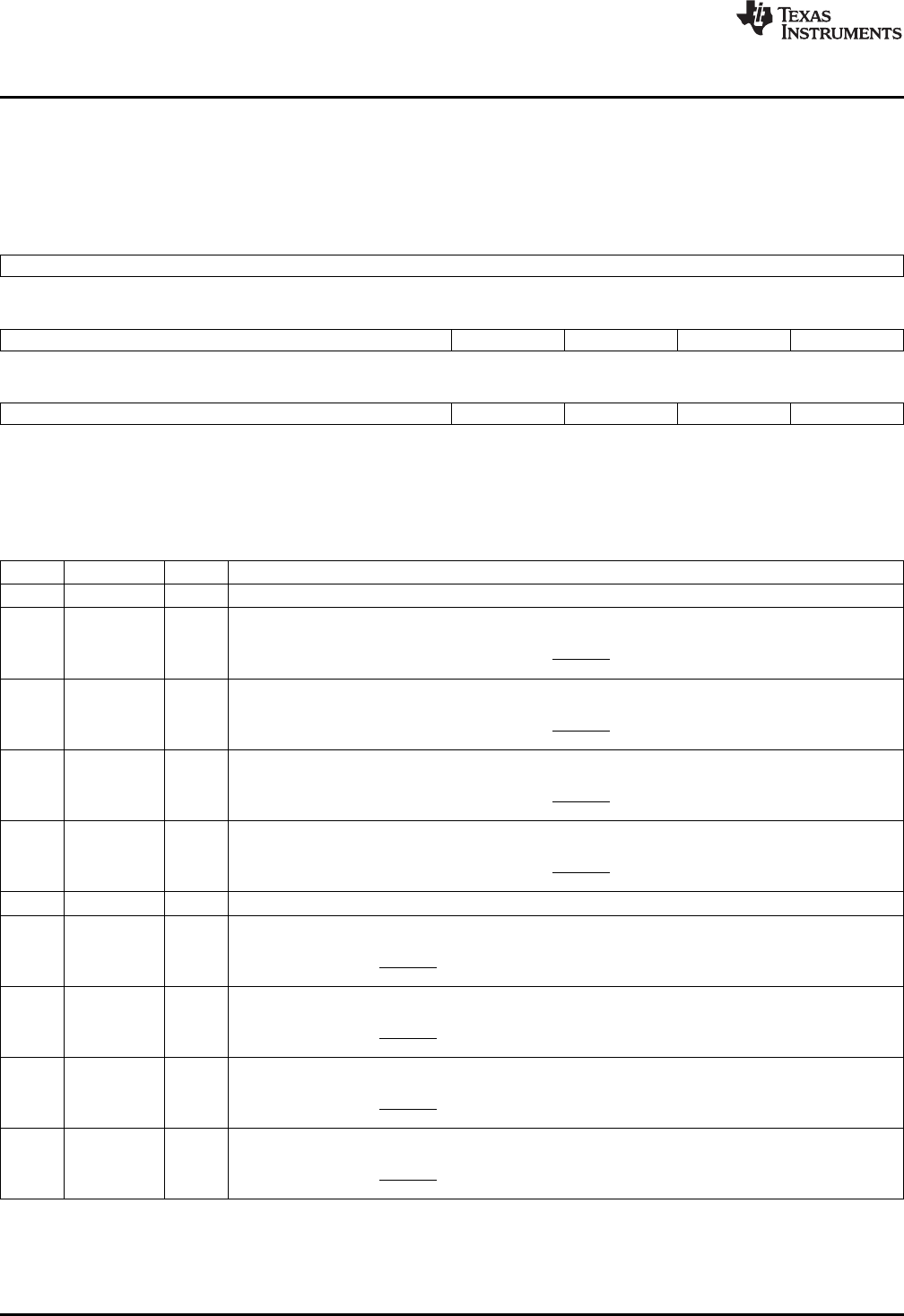

The NAND Flash control register (NANDFCR) is shown in Figure 27 and described in Table 40.

Figure 27. NAND Flash Control Register (NANDFCR)

31 16

Reserved

R-0

15 12 11 10 9 8

Reserved CS5ECC CS4ECC CS3ECC CS2ECC

R-0 R/W-0 R/W-0 R/W-0 R/W-0

7 4 3 2 1 0

Reserved CS5NAND CS4NAND CS3NAND CS2NAND

R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 40. NAND Flash Control Register (NANDFCR) Field Descriptions

Bit Field Value Description

31-12 Reserved 0 Reserved

11 CS5ECC NAND Flash ECC start for chip select 5.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EM_CS5.

10 CS4ECC NAND Flash ECC start for chip select 4.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EM_CS4.

9 CS3ECC NAND Flash ECC start for chip select 3.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EM_CS3.

8 CS2ECC NAND Flash ECC start for chip select 2.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EM_CS2.

7-4 Reserved 0 Reserved

3 CS5NAND NAND Flash mode for chip select 5.

0 Not using NAND Flash.

1 Using NAND Flash on EM_CS5.

2 CS4NAND NAND Flash mode for chip select 4.

0 Not using NAND Flash.

1 Using NAND Flash on EM_CS4.

1 CS3NAND NAND Flash mode for chip select 3.

0 Not using NAND Flash.

1 Using NAND Flash on EM_CS3.

0 CS2NAND NAND Flash mode for chip select 2.

0 Not using NAND Flash.

1 Using NAND Flash on EM_CS2.

60

Asynchronous External Memory Interface (EMIF) SPRUEQ7C–February 2010

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated