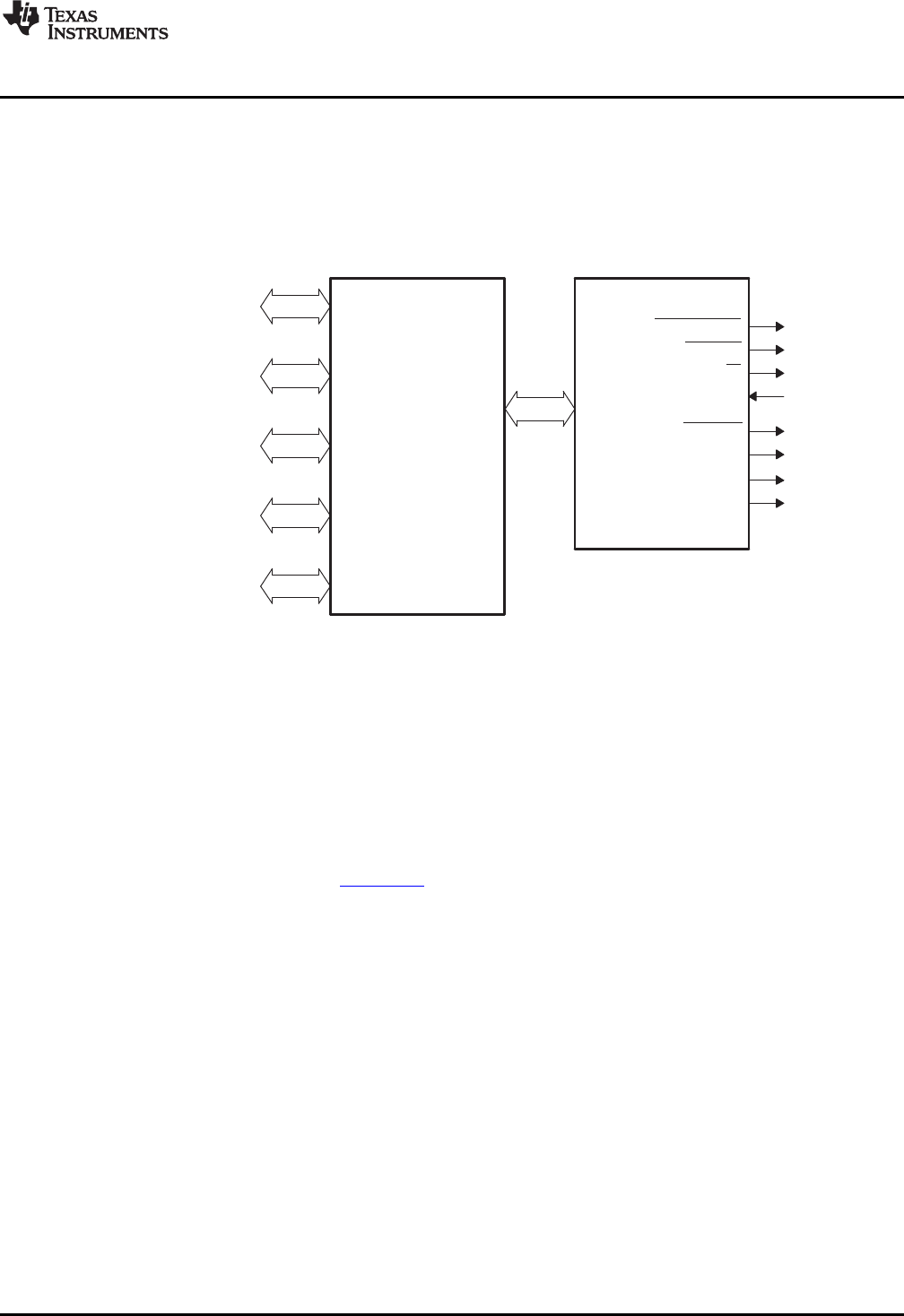

EM_CS[5:2]

EM_OE

EM_RW

EM_WAIT[5:2]

EM_WE

EM_BA[1:0]

EM_D[15:0]

EM_A[22:0]

EMIF

SCR

VICP

DSP

ARM

EDMA3

Master peripherals

www.ti.com

Architecture

1.3 Functional Block Diagram

Figure 1 illustrates the connections between the EMIF and its internal requesters, along with the external

EMIF pins. Section 2.2 contains a description of the entities internal to the device that can send requests

to the EMIF, along with their prioritization. Section 2.3 describes the EMIF's external pins and summarizes

their purpose when interfacing with SDRAM and asynchronous devices.

Figure 1. EMIF Functional Block Diagram

2 Architecture

This section provides details about the architecture and operation of the EMIF.

2.1 Clock Control

The EMIF's internal clock is sourced from the SYSCLK3 clock domain of PLL controller 0 and cannot be

sourced directly from an external input clock. The frequency of the SYSCLK3 clock domain is the PLL0

frequency divided by 4. Changes to the frequency of the input clock to PLL controller 0 and to the PLL

controller 0 multiplier values alters the operating frequency of the EMIF. See the TMS320DM646x DMSoC

ARM Subsystem Reference Guide (SPRUEP9) for more information on how to program the PLL

controller.

2.2 EMIF Requests

Four different sources within the device can make requests to the EMIF. These requests consist of

accesses to asynchronous memory and EMIF memory-mapped registers. Because the EMIF can process

only one request at a time, a high performance switched central resource (SCR) exists to provide

prioritized requests from the different sources to the EMIF. Each requester has a programmable priority

value that may be configured in the System Module MSTPRI0 register or in the EDMACC QUEPRI

register. See the device-specific data manual for more information.

If a request is submitted from two or more sources simultaneously, the SCR will forward the highest

priority request to the EMIF first. Upon completion of a request, the SCR again evaluates the pending

requests and forwards the highest priority pending request to the EMIF.

9

SPRUEQ7C–February 2010 Asynchronous External Memory Interface (EMIF)

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated