10Base-T PHY Registers

A-39

Register Definitions

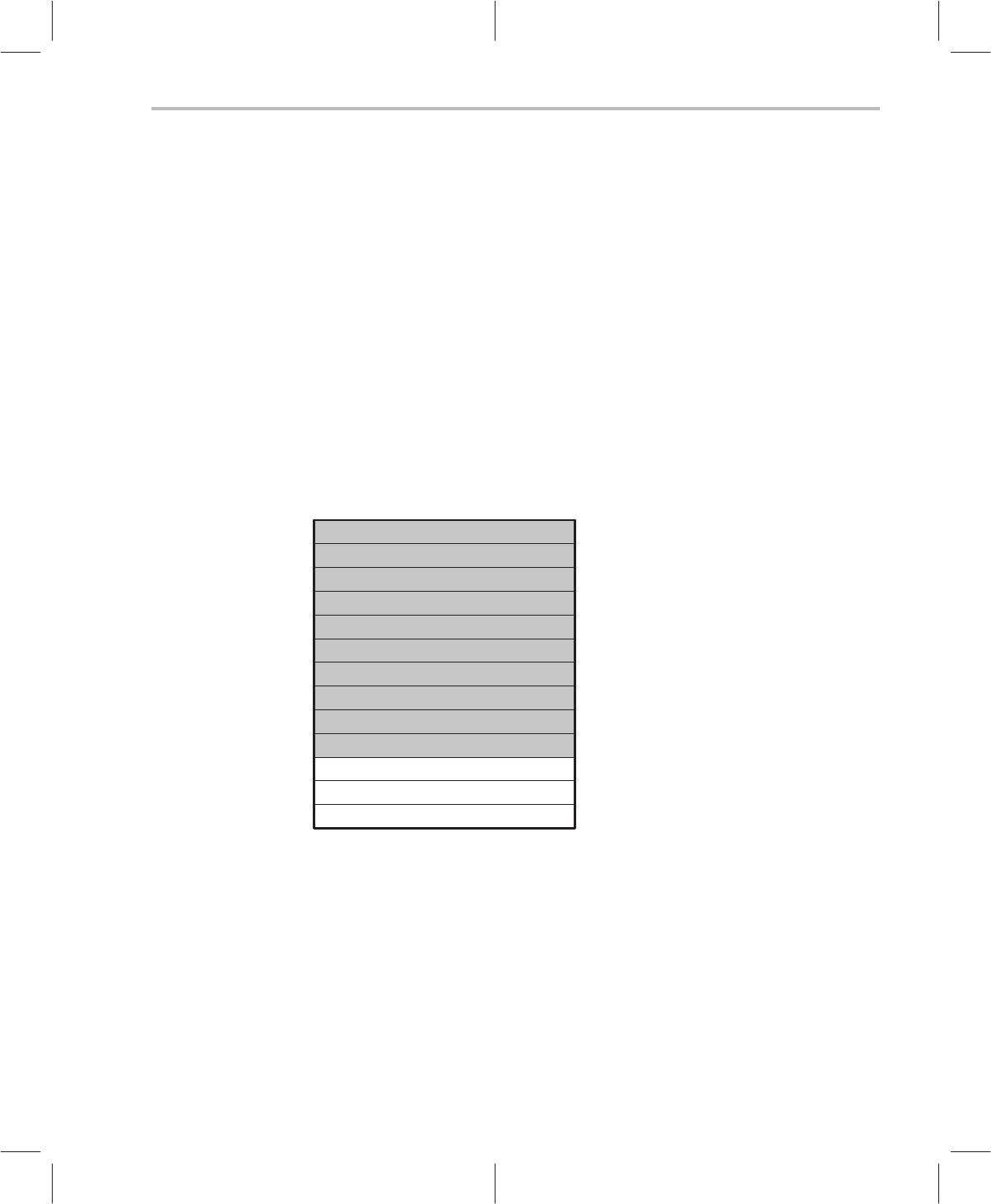

A.4 10Base-T PHY Registers

The 10Base-T PHY registers are indirectly accessible through the MII. This is

a low-speed serial interface which is supported on ThunderLAN through the

NetSio register in adapter DIO space. A host software program uses the

MCLK, MTXEN, and MDATA bits in this register to implement the MII serial pro-

tocol for the management interface.

The 802.3u MII serial protocol allows for up to 32 different PMDs, with up to

32 (16-bit wide) internal registers in each device. The 10Base-T PHY imple-

ments seven internal registers, three of which are hardwired. The diagram be-

low shows the devices register map. The registers shown in gray are the ge-

neric registers mandated by the MII specification. The registers shown in white

are TI-specific registers.

Figure A–8. 10Base-T PHY Registers

GEN_id_lo

GEN_id_hi

GEN_sts

GEN_ctl

Reserved

Reserved

Reserved

AN expansion

AN link-partner ability

AN advertisement

TLPHY_sts

TLPHY_ctl

TLPHY_id

ThunderLAN PHY status register

ThunderLAN PHY identifier

Register

ThunderLAN PHY control register

Reserved by 802.3

Autonegotiation expansion

Autonegotiation link-partner ability

Autonegotiation advertisement

PHY generic identifier (low)

PHY generic identifier (high)

PHY generic status register

PHY generic control register

0x12

0x11

0x10

0x0F

through

0x07

0x06

0x05

0x04

0x03

0x02

0x01

0x00

Description