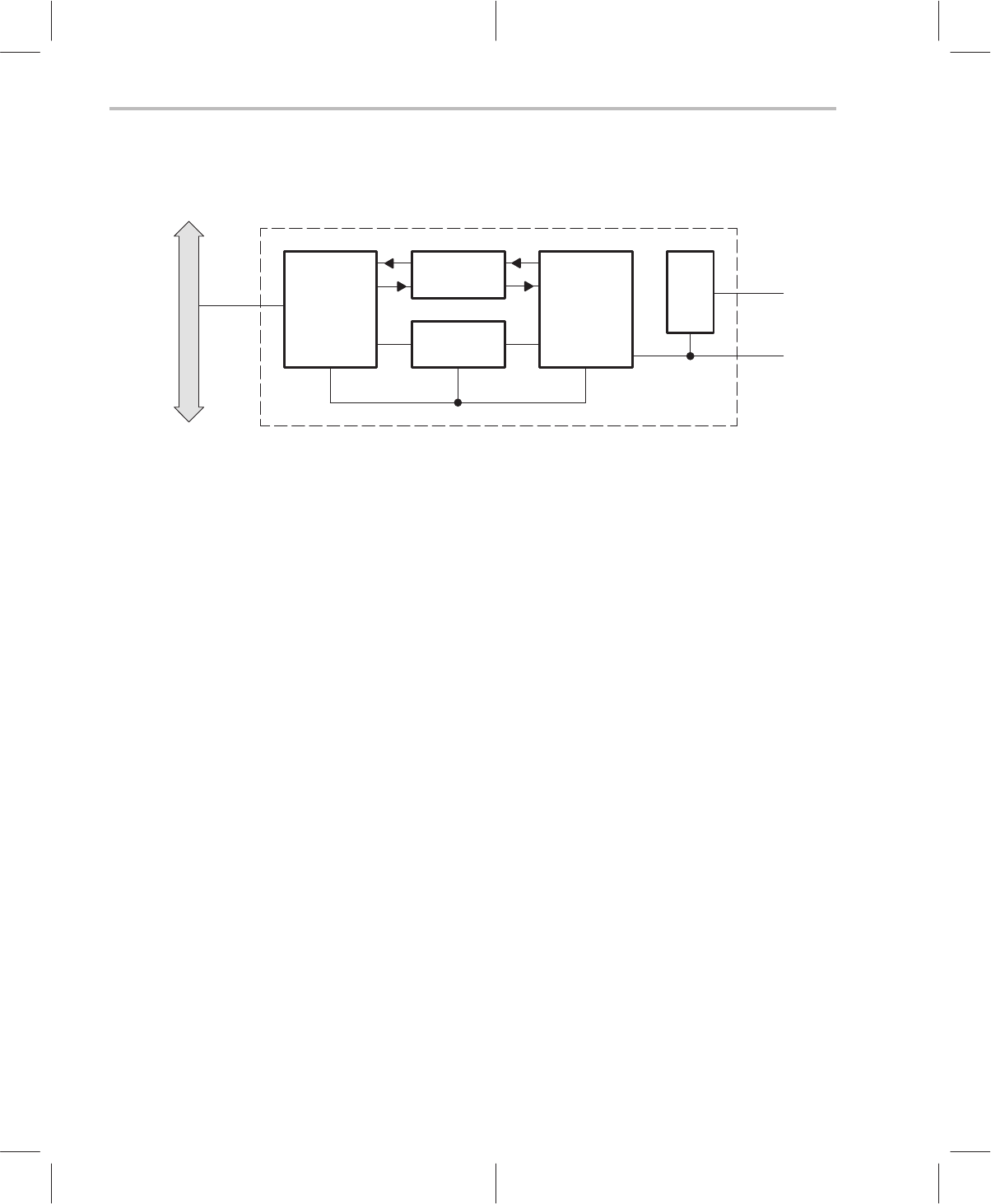

ThunderLAN Architecture

1-2

1.1 ThunderLAN Architecture

Figure 1–1. The ThunderLAN Controller

PCI Bus

PCI

controller

FIFO

registers

Multiplexed

SRAM

LAN

controller

PHY

LAN

802.3

100M-bps

MII

An integrated PHY provides interface functions for 10Base-T carrier sense

multiple access/collision detect (CSMA/CD) (Ethernet). A MII is used to com-

municate with the integrated PHY. The PHY is an independent module from

the rest of the ThunderLAN controller. This allows the PHY to be reset and

placed in a power-down mode.

The PCI controller is responsible for direct memory accesses (DMAs) to and

from the host memory. It is designed to relieve the host from time-consuming

data movements, thereby reducing use of the host CPU. The PCI interface

supports a 32-bit data path.

ThunderLAN supports two transmit and one receive channels. The demand

priority protocol supports two frame priorities: normal and priority. The two

transmit channels provide independent host channels for these two priority

types. CSMA/CD protocols only support a single frame priority, but the two

channels can be used to prioritize network access, if needed. All received

frames pass through the single receive channel.

ThunderLAN’s multiplexed SRAM is 3.375K bytes in size. This allows it to sup-

port one 1.5K byte FIFO for receive, two 0.75K byte FIFOs for the two transmit

(Tx) channels, and three 128-byte lists (see section 5.1, List Management). In

one-channel mode, the two Tx channels are combined, giving a single 1.5K-

byte FIFO for a single Tx channel. Supporting 1.5K byte of FIFO per channel

allows full frame buffering of Ethernet frames. PCI latency is such that a mini-

mum of 500 bytes of storage is required to support 100M-bps LANs. (Refer to

the

PCI Local Bus Specification,

revision 2.0, section 3.5, Latency).

ThunderLAN’s industry-standard MII permits ease of upgrade. External de-

vices can be connected to the MII and managed, if they support the two-wire

management interface. PHY layer functions for 100M-bps CSMA/CD and de-

mand priority are connected to the MII.