PCI Configuration Registers

A-6

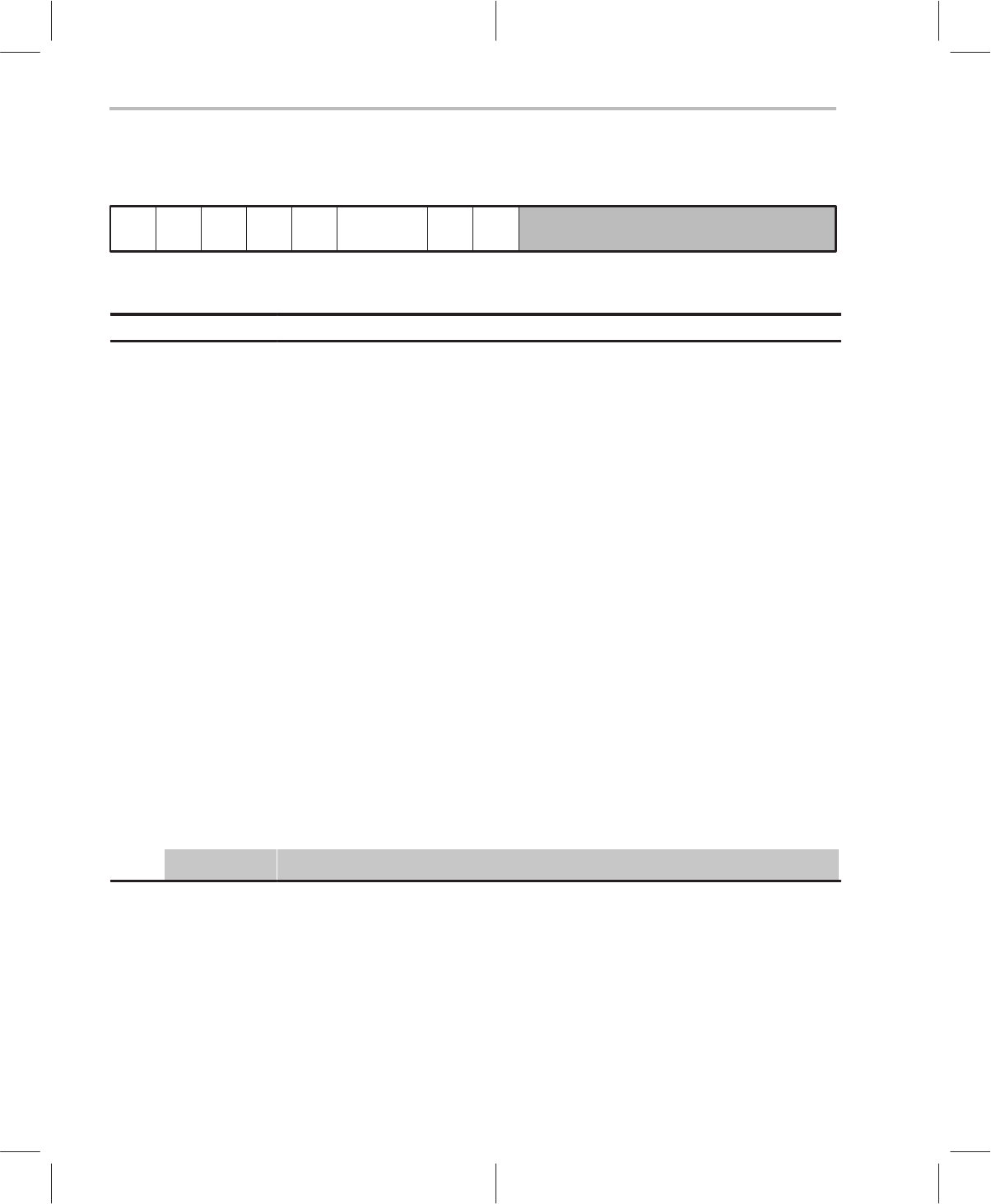

A.1.5 PCI Status Register (@ 06h)

cap

FBB

det

DP

(01b)

DEVSEL

Res

ab

RT

ab

RM

err

SS

err

DP

Reserved

0123456789101112131415

Table A–2. PCI Status Register Bits

Bit Name Function

15 DP_err Detected parity error: Indicates that the adapter has detected a parity error. This bit is

set even if the parity error response bit is not set. This bit can only be set by the adapter,

and only cleared by the host’s writing a 1 to this bit position.

14 SS_err Signaled system error: When set, indicates ThunderLAN has asserted PSERR# due

to an adapter failure. This bit can only be set by the adapter and only be cleared by the

host’s writing a 1 to this bit position.

13 RM_ab Received master abort: When set, indicates ThunderLAN aborted a master cycle with

a master abort. This bit can only be set by the adapter and only be cleared by the host’s

writing a 1 to this bit position.

12 RT_ab Received target abort: When set, indicates a ThunderLAN master cycle was aborted

due to a target abort. This bit can only be set by the adapter, and only be cleared by

the host’s writing a 1 to this bit position.

11 Reserved

10–9 Devsel PDevSel timing: These bits indicate the PDEVSEL# timing supported by ThunderLAN.

These bits are hardwired to 01b, indicating medium speed (2 cycles) decoding of

PDEVSEL#.

8 DP_det Data parity detect

:

When set, indicates PPERR# is asserted for a cycle for which the

adapter was the bus master and the parity error response bit is set. (This bit is set if

the target signals PPERR# on an adapter master cycle.) This bit can only be set by the

adapter and can only be cleared by the host’s writing a 1 to this bit position.

7 FBB_cap Fast back-to-back capable: This bit is hardwired to a 1 to indicate that ThunderLAN can

receive fast back-to-back cycles to different agents.

6 – 0

Reserved Writes to these bits are ignored, bits are always read as zero.