Remote Operation

4–56 TM-XDOP-01XN

Error/Event Queue (ERR)

This bit it TRUE if any errors are present in the Error/Event Queue.

Questionable Status Register Summary (QSR)

This bit is TRUE when a bit in the Questionable Event Status Register is set and

its corresponding bit in the Questionable Status Enable Register is TRUE.

Message Available (MAV)

This bit is TRUE whenever the power supply is ready to accept a request by the

Digital Programming Interface to output data bytes. This message is FALSE when

the output queue is empty.

Standard Event Status Summary (ESB)

This bit is TRUE when a bit is set in the Standard Event Status Register.

Master Summary Status (MSS)

This is caused by one of the following:

• Status Byte bit 0 AND Service Request Enable Register bit 0

• Status Byte bit 1 AND Service Request Enable Register bit 1

• Status Byte bit 2 AND Service Request Enable Register bit 2

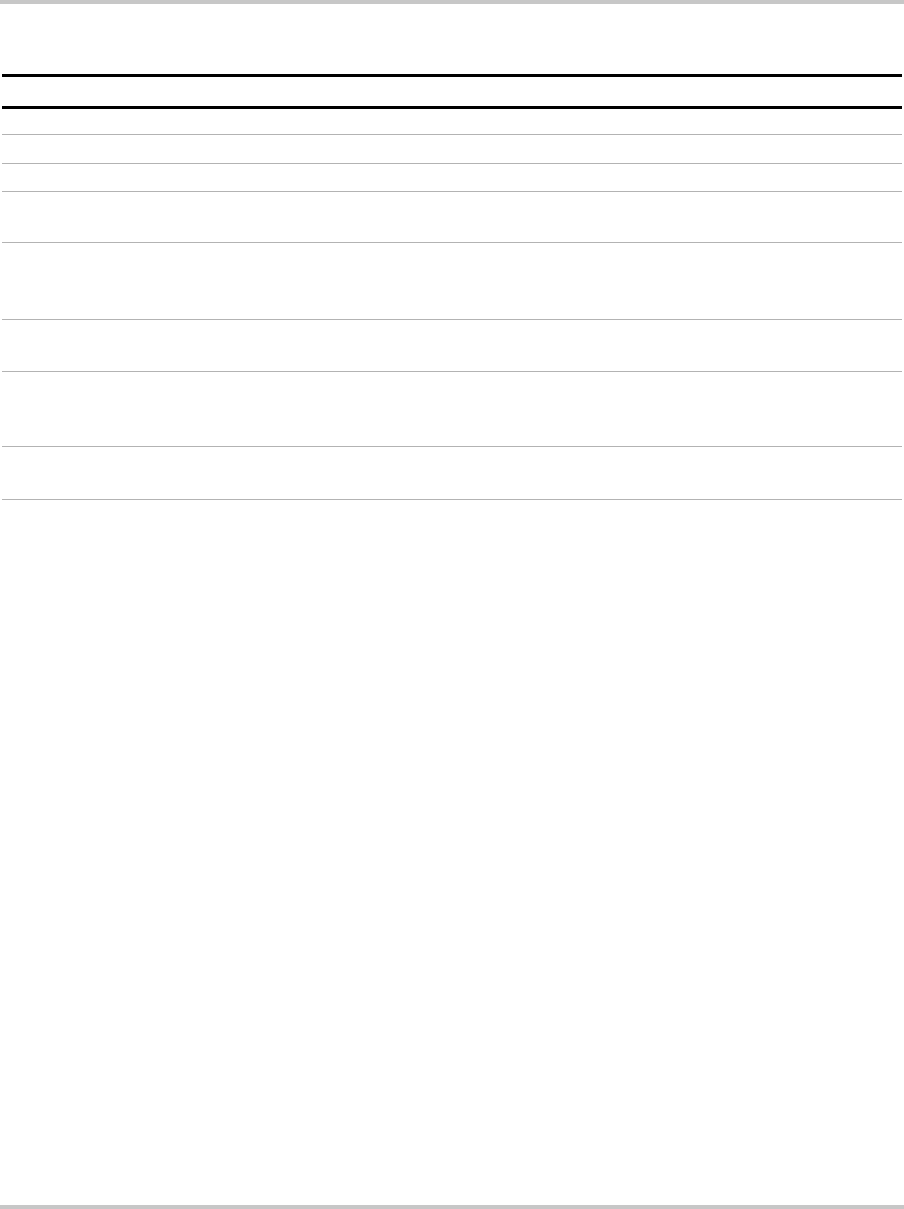

Table 4-21

Status Byte Summary Register

Bit Bit Weight Bit Name Description

01 Reserved

12 Reserved

2 4 Error/Event Queue (ERR) Set if any errors are present in the Error/Event queue.

3 8 Questionable Status

Register (QSR)

Set if any bits are set in the Questionable Status Event

register.

4 16 Message Available (MAV) Indicates whether the output queue is empty. MAV is

TRUE if the device is ready to accept a request from the

controller.

5 32 Standard Event Status Bit

Summary (ESB)

A summary of the Standard Event Status Register.

6 64 Request Service (RQS)

Master Status Summary

(MSS)

MSS indicates that the device has at least one reason for

requesting service.

7 128 Operation Status Register

(OSR)

Present if a bit is set in the Operation status register.

TM-XDOP-01XN.book Page 56 Monday, July 17, 2006 11:19 AM