Technical Reference Guide

Compaq Deskpro EN Series of Personal Computers

Desktop and Minitower Form Factors

Third Edition - September 1998

3-5

3.2.2 PROCESSOR CHANGING/UPGRADING

The slot 1 design allows for easy changing and/or upgrading of the processor/cache complex.

Changing the processor requires disconnection/re-connection of the heat sink sensor cable and

may require upgrading the BIOS firmware and re-configuration of the bus/core speed switch

discussed in the following paragraphs.

3.2.2.1 BIOS Upgrading

The Pentium II 450 and Celeron 300A/333 processors require BIOS firmware dated 7/30/98 or

later. Installing and running one of these processors in a system with BIOS dated earlier than

7/30/98 will likely cause the system to halt (lockup).

The BIOS (ROM) version may be checked using either the Compaq Diagnostics or Compaq

Insight utility.

3.2.2.2 Processor Speed Selection

Changing the processor may require re-configuration of the bus/core frequency ratio. The system

board includes a six-position DIP switch (SW), of which positions 2-5 are read by the processor

(while RESET- is active) to select the bus-to-core frequency ratio. Table 3-2 shows the possible

switch configurations for this system and the resultant core (or processing) frequency, based on

the front side bus (FSB or Host bus) frequency.

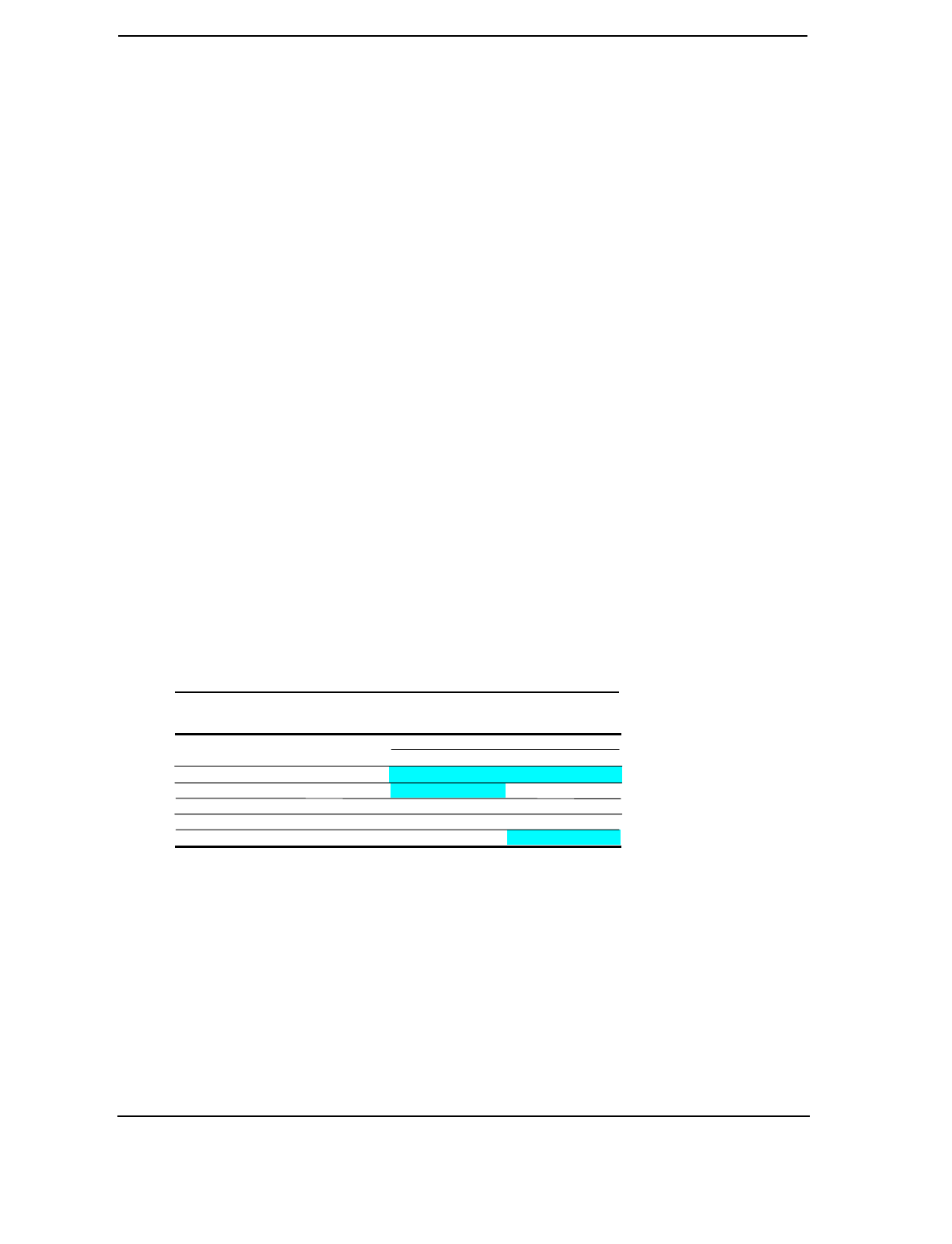

Table 3–2.

Bus/Core Speed Switch Settings

Table 3-2.

Bus/Core Speed Switch Settings

DIP SW1 Settings

2 3 4 5 [1]

Bus/Core

Freq. Ratio w/66-MHz FSB w/100-MHz FSB

1 0 0 0 1/3 200 300

1 1 0 0 2/7 233 350

0 0 1 0 1/4 266 400

0 1 1 0 2/9 300 450

1 0 1 0 1/5 333 500

NOTES:

Shipping configurations are unshaded.

[1] 0 = Switch Closed (On), 1 = Switch Open (Off)

The DIP switch settings should be set to match the processor installed.

Configuring for a speed higher than that which the processor is

designed could result in unreliable operation and possible system damage.

The processor sets the clock generator to the appropriate bus frequency. Software can determine

the operating speed by reading the bus speed from an MSR register in the processor.

Core Frequency