Chapter 4 System Support

Compaq Deskpro EN Series of Personal Computers

Desktop and Minitower Form Factors

Third Edition - September 1998

4-22

The RAM refresh is designed to perform a memory read cycle on each of the 512 row addresses

in the DRAM memory space. Refresh operations are used to refresh memory on the 32-bit

memory bus and the ISA bus. The refresh address is provided on lines SA00 through SA08.

Address lines LA23..17, SA18,19 are driven low.

The remaining address lines are in an undefined state during the refresh cycle. The refresh

operations are driven by a 69.799-KHz clock generated by Interval Timer 1, Counter 1. The

refresh rate is 128 refresh cycles in 2.038 ms.

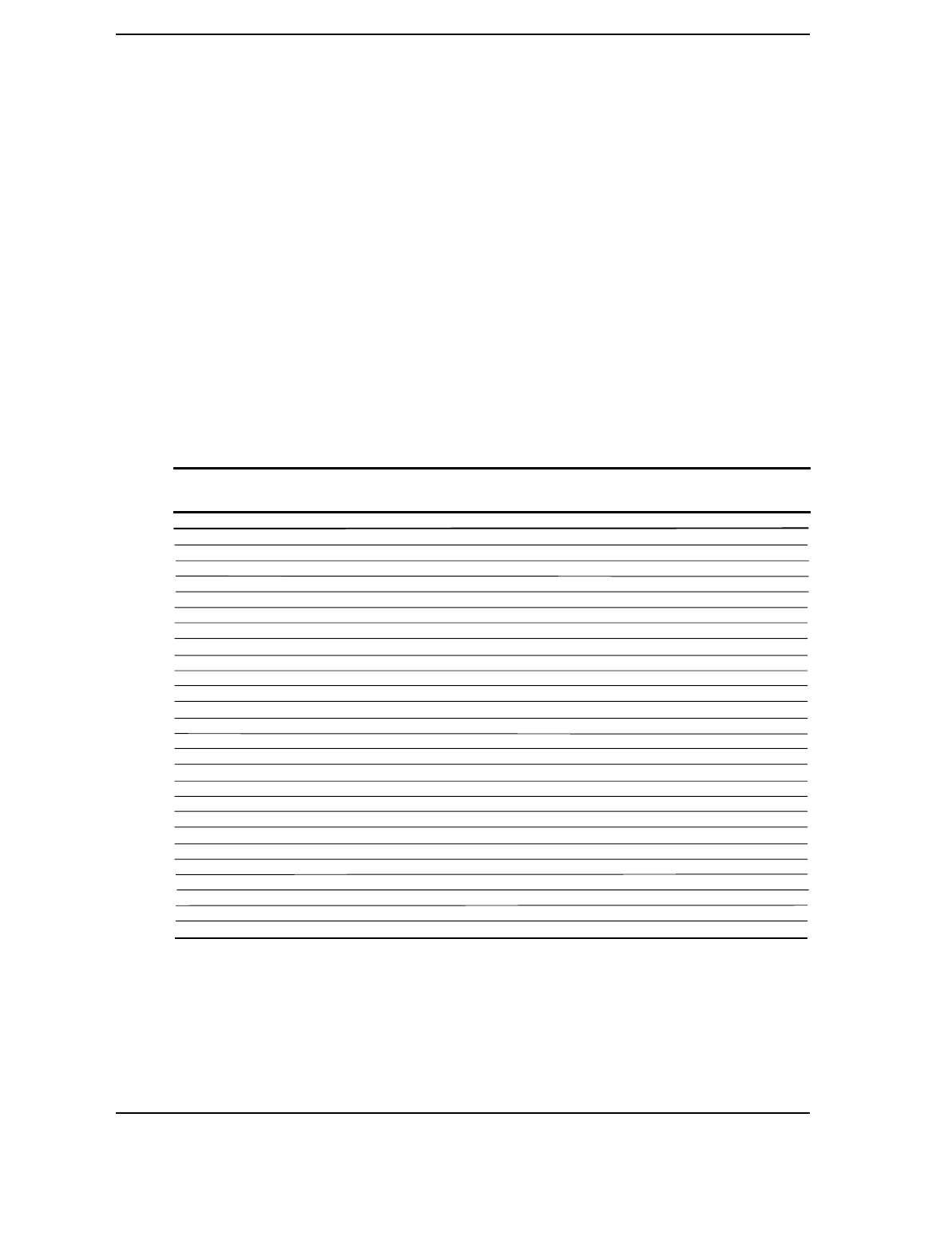

4.4.3.2 DMA Controller Registers

Table 4-12 lists the DMA Controller Registers and their I/O port addresses. Note that there is a

set of registers for each DMA controller.

Table 4–12.

DMA Controller Registers

Table 4-12.

DMA Controller Registers

Register Controller 1 Controller 2 R/W

Status 008h 0D0h R

Command 008h 0D0h W

Mode 00Bh 0D6h W

Write Single Mask Bit 00Ah 0D4h W

Write All Mask Bits 00Fh 0DEh W

Software DRQx Request 009h 0D2h W

Base and Current Address - Ch 0 000h 0C0h W

Current Address - Ch 0 000h 0C0h R

Base and Current Word Count - Ch 0 001h 0C2h W

Current Word Count - Ch 0 001h 0C2h R

Base and Current Address - Ch 1 002h 0C4h W

Current Address - Ch 1 002h 0C4h R

Base and Current Word Count - Ch 1 003h 0C6h W

Current Word Count - Ch 1 003h 0C6h R

Base and Current Address - Ch 2 004h 0C8h W

Current Address - Ch 2 004h 0C8h R

Base and Current Word Count - Ch 2 005h 0CAh W

Current Word Count - Ch 2 005h 0CAh R

Base and Current Address - Ch 3 006h 0CCh W

Current Address - Ch 3 006h 0CCh R

Base and Current Word Count - Ch 3 007h 0CEh W

Current Word Count - Ch 3 007h 0CEh R

Temporary (Command) 00Dh 0DAh R

Reset Pointer Flip-Flop (Command) 00Ch 0D8h W

Master Reset (Command) 00Dh 0DAh W

Reset Mask Register (Command) 00Eh 0DCh W

NOTE:

For a detailed description of the DMA registers, refer to the

Compaq EISA Technical Reference Guide

.