Chapter 4 System Support

Compaq Deskpro EN Series of Personal Computers

Desktop and Minitower Form Factors

Third Edition - September 1998

4-20

4.4.3 DIRECT MEMORY ACCESS

Direct Memory Access (DMA) is a method by which an ISA device accesses system memory

without involving the microprocessor. DMA is normally used to transfer blocks of data to or from

an ISA I/O device. DMA reduces the amount of CPU interactions with memory, freeing the CPU

for other processing tasks.

NOTE:

This section describes DMA in general. For detailed information regarding

DMA operation, refer to the Compaq Extended Industry Standard Architecture (EISA)

Technical Reference Guide. Note, however, that EISA enhancements as described in the

referenced document are not supported in this (ISA only) system.

The South Bridge component includes the equivalent of two 8237 DMA controllers cascaded

together to provide eight DMA channels. Table 4-10 lists the default configuration of the DMA

channels.

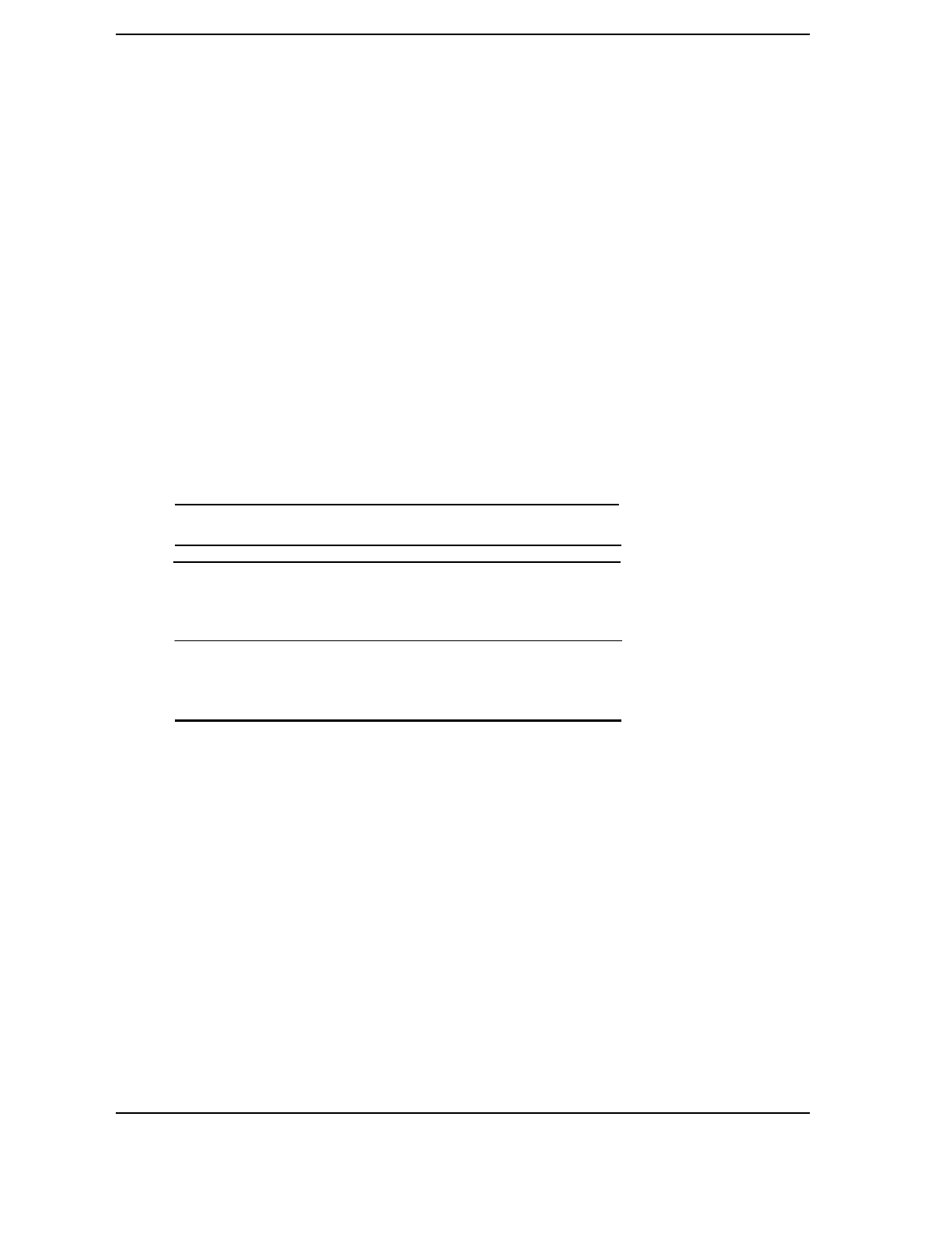

Table 4–10.

Default DMA Channel Assignments

Table 4-10.

Default DMA Channel Assignments

DMA Channel Device ID

Controller 1 (byte transfers)

0

1

2

3

Spare & ISA conn. pins D8, D9

Audio subsystem & ISA conn. pins B17, B18

Diskette drive & ISA conn. pins B6, B26

ECP LPT1 & ISA conn. pins B15, B16

Controller 2 (word transfers)

4

5

6

7

Cascade for controller 1

Spare & ISA conn. pins D10, D11

Spare & ISA conn. pins D12, D13

Spare & ISA conn. pins. D14, D15

All channels in DMA controller 1 operate at a higher priority than those in controller 2. Note

that channel 4 is not available for use other than its cascading function for controller 1. The

DMA controller 2 can transfer words only on an even address boundary. The DMA controller

and page register define a 24-bit address that allows data transfers within the address space of

the CPU. The DMA controllers operate at 8 MHz.

The DMA logic is accessed through two types of I/O mapped registers; page registers and

controller registers. The mapping is the same regardless of the support chipset used.