CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 42 of 83

15.3 SPI Interface Pins

The SPI interface uses the P1.3–P1.6 pins. These pins are configured using the P1.3 and P1.4–P1.6 Configuration.

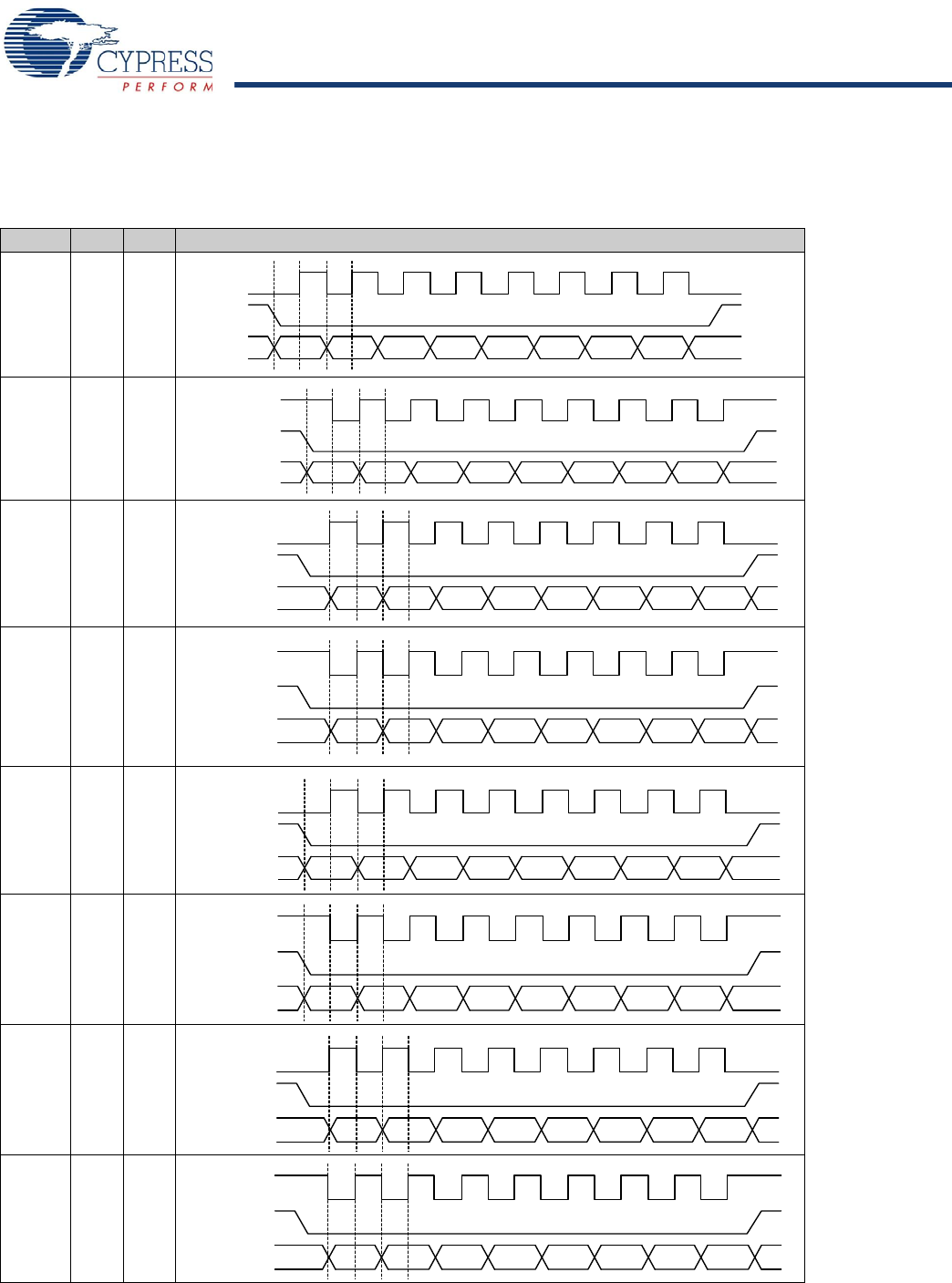

Table 15-4. SPI Mode Timing vs. LSB First, CPOL and CPHA

LSB First CPHA CPOL Diagram

000

001

010

011

100

101

110

111

SCLK

SSEL

DATA

X XMSB Bit 2Bit 3Bit 4Bit 5Bit 6Bit 7 LSB

SCLK

SSEL

X X

DATA

MSB Bit 2Bit 3Bit 4Bit 5Bit 6Bit 7 LSB

SCLK

SSEL

X X

DATA

MSB Bit 2Bit 3Bit 4Bit 5Bit 6Bit 7 LSB

SCLK

SSEL

DATA

X X

MSB Bit 2Bit 3Bit 4Bit 5Bit 6Bit 7 LSB

SCLK

SSEL

DATA

X X

MSBBit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7LSB

SCLK

SSEL

X X

DATA

MSBBit 2 Bit 3 Bit 4 B it 5 Bit 6 Bit 7LSB

SCLK

SSEL

X X

DATA

MSBBit 2Bit 3Bit 4Bit 5Bit 6Bit 7LSB

SCLK

SSEL

DATA

X MSB XBit 2 Bit 3 Bit 4 B it 5 Bit 6 B it 7LSB

[+] Feedback [+] Feedback