CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 51 of 83

17.2 Interrupt Processing

The sequence of events that occur during interrupt processing

follows:

1. An interrupt becomes active, because:

a. The interrupt condition occurs (for example, a timer expires).

b. A previously posted interrupt is enabled through an update

of an interrupt mask register.

c. An interrupt is pending and GIE is set from 0 to 1 in the CPU

Flag register.

2. The current executing instruction finishes.

3. The internal interrupt is dispatched, taking 13 cycles. During

this time, the following actions occur: the MSB and LSB of

Program Counter and Flag registers (CPU_PC and CPU_F)

are stored onto the program stack by an automatic CALL

instruction (13 cycles) generated during the interrupt

acknowledge process.

a. The PCH, PCL, and Flag register (CPU_F) are stored onto

the program stack (in that order) by an automatic CALL

instruction (13 cycles) generated during the interrupt

acknowledge process

b. The CPU_F register is then cleared. Because this clears the

GIE bit to 0, additional interrupts are temporarily disabled.

c. The PCH (PC[15:8]) is cleared to zero.

d. The interrupt vector is read from the interrupt controller and

its value placed into PCL (PC[7:0]). This sets the program

counter to point to the appropriate address in the interrupt

table (for example, 0004h for the POR/LVD interrupt).

4. Program execution vectors to the interrupt table. Typically, a

LJMP instruction in the interrupt table sends execution to the

user's Interrupt Service Routine (ISR) for this interrupt.

5. The ISR executes. Note that interrupts are disabled because

GIE = 0. In the ISR, interrupts are re-enabled by setting

GIE = 1 (care must be taken to avoid stack overflow).

6. The ISR ends with a RETI instruction which restores the

Program Counter and Flag registers (CPU_PC and CPU_F).

The restored Flag register re-enables interrupts, because

GIE = 1 again.

7. Execution resumes at the next instruction, after the one that

occurred before the interrupt. However, if there are more

pending interrupts, the subsequent interrupts are processed

before the next normal program instruction.

17.3 Interrupt Trigger Conditions

Trigger conditions for most interrupts in Table 17-1 on page 50

have been explained in the relevant sections. However,

conditions under which the USB Active (interrupt address 0030h)

and PS2 Data Low (interrupt address 004Ch) interrupts are

triggered are explained follow.

1. USB Active Interrupt: Triggered when the D+/- lines are in a

non-idle state, that is, K-state or SE0 state.

2. PS2 Data Low Interrupt: Triggered when SDATA becomes low

when the SDATA pad is in the input mode for at least 6-7

32 kHz cycles.

3. The GPIO interrupts are edge triggered.

17.4 Interrupt Latency

The time between the assertion of an enabled interrupt and the

start of its ISR is calculated from the following equation.

Latency = Time for current instruction to finish + Time for internal

interrupt routine to execute + Time for LJMP instruction in

interrupt table to execute.

For example, if the 5 cycle JMP instruction is executing when an

interrupt becomes active, the total number of CPU clock cycles

before the ISR begins is as follows:

(1 to 5 cycles for JMP to finish) + (13 cycles for interrupt routine)

+ (7 cycles for LJMP) = 21 to 25 cycles.

In the previous example, at 24 MHz, 25 clock cycles take

1.042 μs.

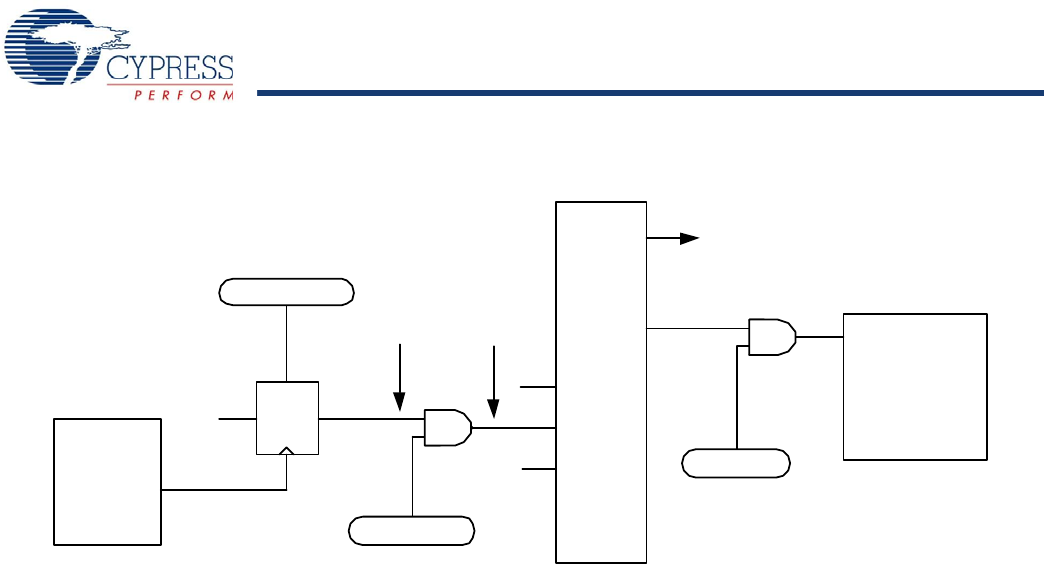

Figure 17-1. Interrupt Controller Block Diagram

Interrupt

Source

(Timer,

GPIO, etc.)

Interrupt Taken

or

Posted

Interrupt

Pending

Interrupt

GIE

Interrupt Vector

Mask Bit Setting

D

R

Q1

Priority

Encoder

M8C Core

Interrupt

Request

...

INT_MSKx

INT_CLRx Write

CPU_F[0]

...

[+] Feedback [+] Feedback