CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 64 of 83

1101 IN x x x STALL Stall IN

NAK IN

1100 OUT x x x Ignore

1100 IN x x x NAK If Enabled NAK IN

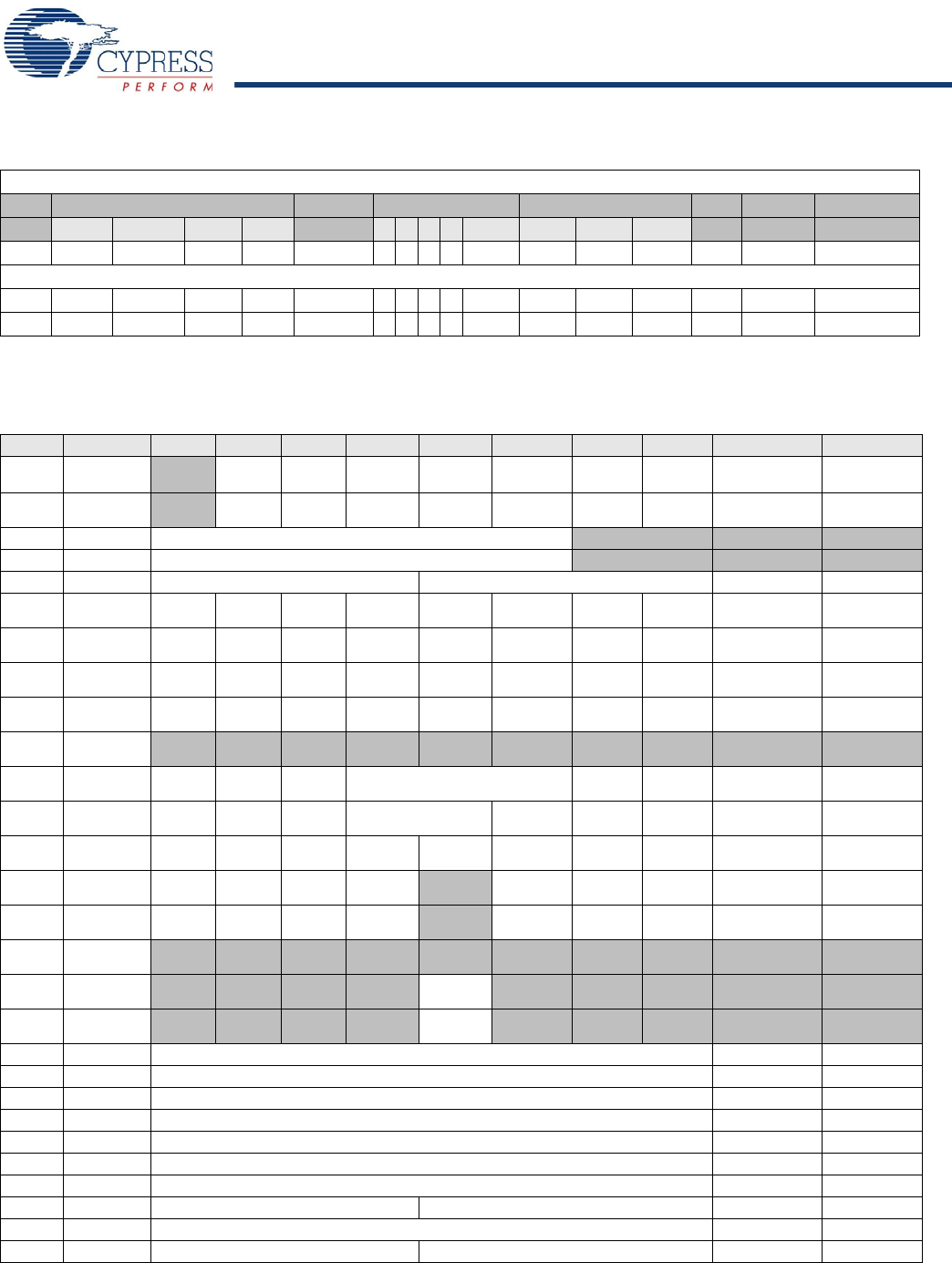

23. Details of Mode for Differing Traffic Conditions

(continued)

Control Endpoint

SIE Bus Event SIE EP0 Mode Register EP0 Count Register EP0 Interrupt Comments

Mode Token Count Dval D0/1 Response S I O A MODE DTOG DVAL COUNT FIFO

24. Register Summary

The XIO bit in the CPU Flags Register must be set to access the extended register space for all registers above 0xFF.

Addr Name 7 6 5 4 3 2 1 0 R/W Default

00 P0DATA

P0.7 P0.6/TIO1 P0.5/TIO0 P0.4/INT2 P0.3/INT1 P0.2/INT0 P0.1/CLK-

OUT

P0.0/CLKI

N

bbbbbbbb 00000000

01 P1DATA

P1.7 P1.6/SMI

SO

P1.5/SMO

SI

P1.4/SCLK P1.3/SSEL P1.2/VREG P1.1/D– P1.0/D+ bbbbbbbb 00000000

02 P2DATA Res

P2.1–P2.0 bbbbbbbb 00000000

03 P3DATA Res

P3.1–P3.0 bbbbbbbb 00000000

04 P4DATA Res Res ----bbbb 00000000

05 P00CR Reserved Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

06 P01CR CLK

Output

Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

bbbbbbbb 00000000

07–09 P02CR–

P04CR

Reserved Reserved Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

--bbbbbb 00000000

0A–0B P05CR–

P06CR

TIO

Output

Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

bbbbbbbb 00000000

0C P07CR

Reserved Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

0D P10CR Reserved Int

Enable

Int Act

Low

Reserved PS/2 Pull

up Enable

Output

Enable

-bb---bb 00000000

0E P11CR Reserved Int

Enable

Int Act

Low

Reserved Open Drain Reserved Output

Enable

-bb--b-b 00000000

0F P12CR

CLK

Output

Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

bbbbbbbb 00000000

10 P13CR Reserved Int

Enable

Int Act

Low

3.3V Drive

High Sink Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

11–13 P14CR–

P16CR

SPI Use Int

Enable

Int Act

Low

3.3V Drive

High Sink Open Drain Pull up

Enable

Output

Enable

bbbbbbbb 00000000

14 P17CR

Reserved Int

Enable

Int Act

Low

TTL Thresh High Sink Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

15 P2CR

Reserved Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

16 P3CR

Reserved Int

Enable

Int Act

Low

TTL Thresh Reserved Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

20 FRTMRL Free Running Timer [7:0] bbbbbbbb 00000000

21 FRTMRH Free Running Timer [15:8] bbbbbbbb 00000000

22 TCAP0R Capture 0 Rising [7:0] bbbbbbbb 00000000

23 TCAP1R Capture 1 Rising [7:0] bbbbbbbb 00000000

24 TCAP0F Capture 0 Falling [7:0] bbbbbbbb 00000000

25 TCAP1F Capture 1 Falling [7:0] bbbbbbbb 00000000

26 PITMRL Prog Interval Timer [7:0] bbbbbbbb 00000000

27 PITMRH Reserved Prog Interval Timer [11:8] ----bbbb 00000000

28 PIRL Prog Interval [7:0] bbbbbbbb 00000000

29 PIRH Reserved Prog Interval [11:8] ----bbbb 00000000

[+] Feedback [+] Feedback