S1F76600 Series

1–8 EPSON S1F70000 Series

Technical Manual

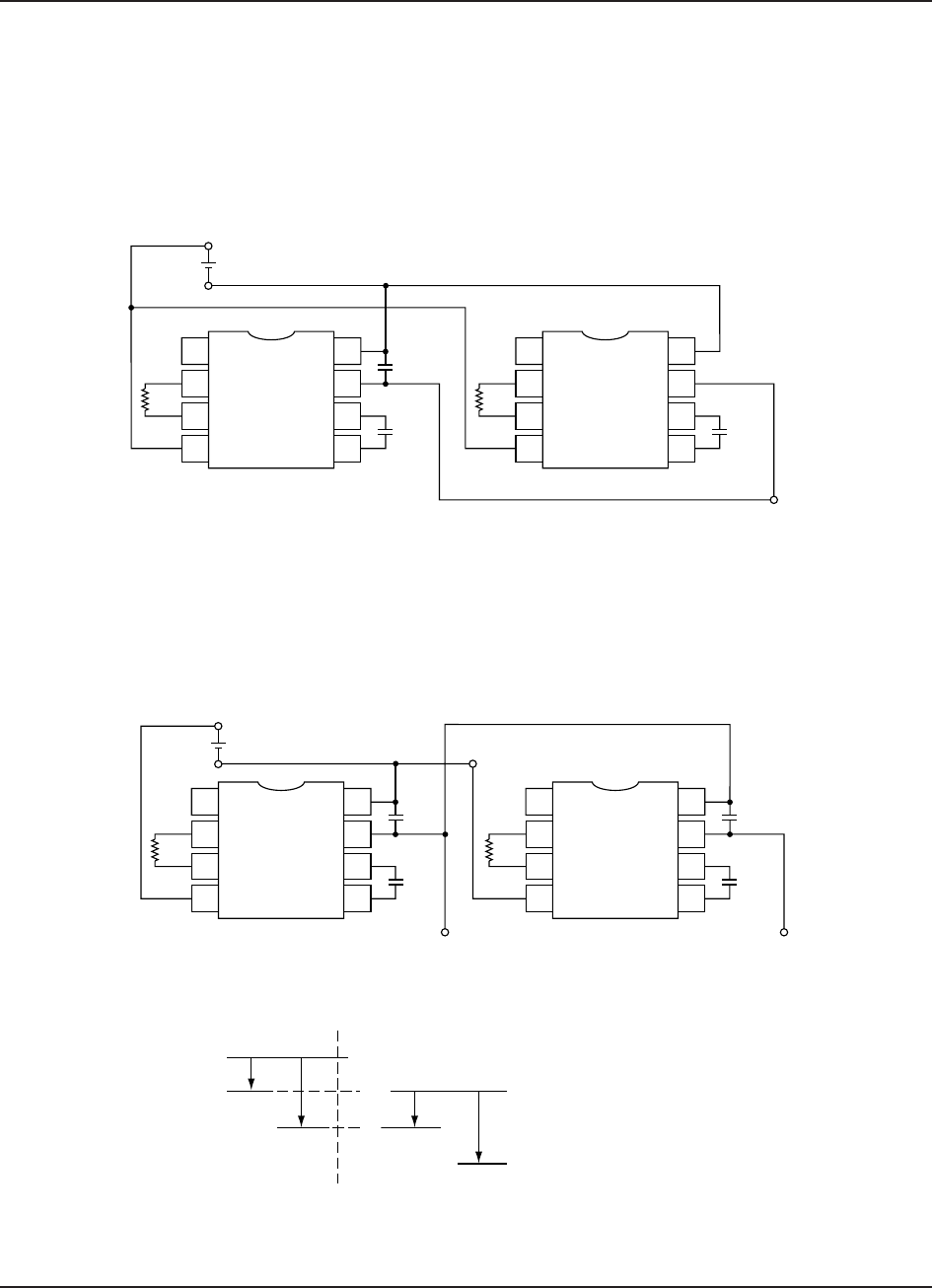

TYPICAL APPLICATIONS

Parallel Connection

Connecting two or more chips in parallel reduces the

output impedance by 1/n, where n is the number of de-

vices used.

5 V

C1

10µF

C2

10µF

V

DD

= 0 V

V

I

= –5 V

V

O

= –10 V

1MΩ

+

+

8

7

6

5

1

2

3

4

C1

10µF

1MΩ

+

8

7

6

5

1

2

3

4

Serial Connection

Connecting two or more chips in series obtains a higher

output voltage than can be obtained using a parallel

connection, however, this also raises the output imped-

ance.

Potential levels

5 V

C1

10µF

C2

10µF

V

DD

= 0 V

V

I

= –5 V

V

O

' = –15 V

V

O

= –10 V = V

I

'

V

DD

' = V

I

= –5

1MΩ

+

+

8

7

6

5

1

2

3

4

C1

10µF

C2

10µF

1MΩ

+

+

8

7

6

5

1

2

3

4

V

DD

(0 V)

V

I

(–5 V)

V

O

(–10 V)

Primary stage Secondary stage

V

DD

'

V

I

'

V

O

' (–15 V)