Chapter 1. Technical description 13

1.4.1 Intel Xeon Processor MP

The Xeon Processor MP (code named “Foster” or “Gallatin”) returns to the ZIF

socket design of the original Pentium processor, instead of the Slot 2 cartridge

design of the Pentium III Xeon processors. This smaller form factor means that

the x440 can have up to eight processors in a 4U node.

The Xeon MP processor has three levels of cache, all of which are on the

processor die:

Level 3 cache is equivalent to L2 cache on the Pentium III Xeon. Foster

processors in the x440 models contain either 512 KB or 1 MB of L3 cache.

Gallatin processors contain either 1 MB or 2 MB or L3 cache.

Level 2 cache is equivalent to L1 cache on the Pentium III Xeon and is 256 KB

in size. The L2 cache implements the Advanced Transfer Cache technology,

which means L2-to-processor transfers occur across a 256-bit bus in only one

clock cycle.

A new level 1 cache, 12 KB in size, is “closest” to the processor and is used to

store micro-operations (that is, decoded executable machine instructions) and

serves those to the processor at rated speed. This additional level of cache

saves decode time on cache hits. There is an additional 8 KB for data related

to those instructions, for a total of 20KB.

The x440 also implements a Level 4 cache as described in 1.6, “IBM XceL4

Server Accelerator Cache” on page 19.

Intel has also introduced a number of features associated with its newly

announced NetBurst micro-architecture. These are available in the x440,

including:

400 MHz frontside bus

The Pentium III Xeon processor has a 100 MHz frontside bus that equates to

a burst throughput of 800 MBps. With protocols such as TCP/IP, this has been

shown to be a bottleneck in high-throughput situations. The Xeon Processor

MP improves on this by using two 100 MHz clocks, out of phase with each

other by 90° and using both edges of each clock to transmit data. This is

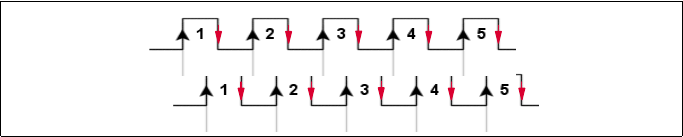

shown in Figure 1-8.

Figure 1-8 Quad-pumped frontside bus

100 MHz clock A

100 MHz clock B