Chapter 2. Positioning 45

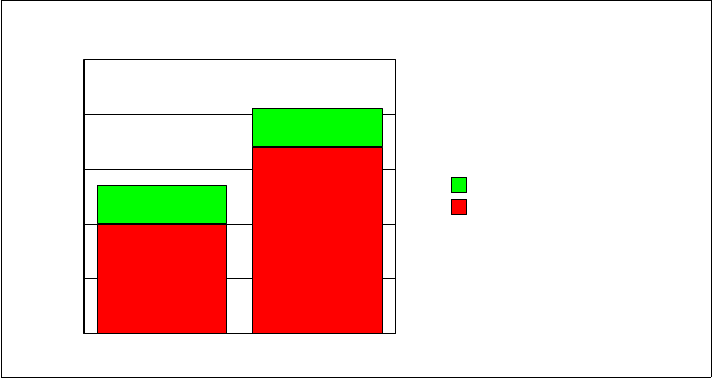

Figure 2-3 Comparing processor performance

The three-level cache architecture of the Xeon MP processor delivers the

following benefits compared to Xeon PIII processor:

– Higher throughput: Peak bandwidth of 51.2 GBps compared to 28.8 GBps

for Xeon PIII processor.

– Improved average cache hit rates due to larger cache line sizes. Line size

of 128-bytes compared to 32-bytes for the Xeon PIII processor.

Advanced Dynamic Execution

The Pentium III Xeon processor has a 10-stage pipeline. However, the large

number of transistors in each pipeline stage means that the processor is

limited to speeds under 1 GHz due to latency in the pipeline.

The Xeon Processor MP has a 20-stage pipeline, which can hold up to 126

concurrent instructions inflight and up to 48 reads and 24 writes active in the

pipeline. Faster raw execution results in higher transaction rates and faster

response times for Web and database servers.

Intel reports that the Xeon MP processor supports 36% more users and can

process 40% more orders in an e-business environment than supported and

processed in the Pentium III Xeon processor.

The Xeon DP is similar to the Xeon MP and is also based on the Intel NetBurst

micro-architecture. The Xeon DP was designed by Intel to only support two-way

SMP. However, with the use of the IBM XA-32 chipset, the x440 can have up to

four Xeon DP processors installed.

One-way Two-way

Hyper-Threading delta

Physical processor

Performance with & without Hyper-Threading