88 Software Developer’s Manual

PCI Local Bus Interface

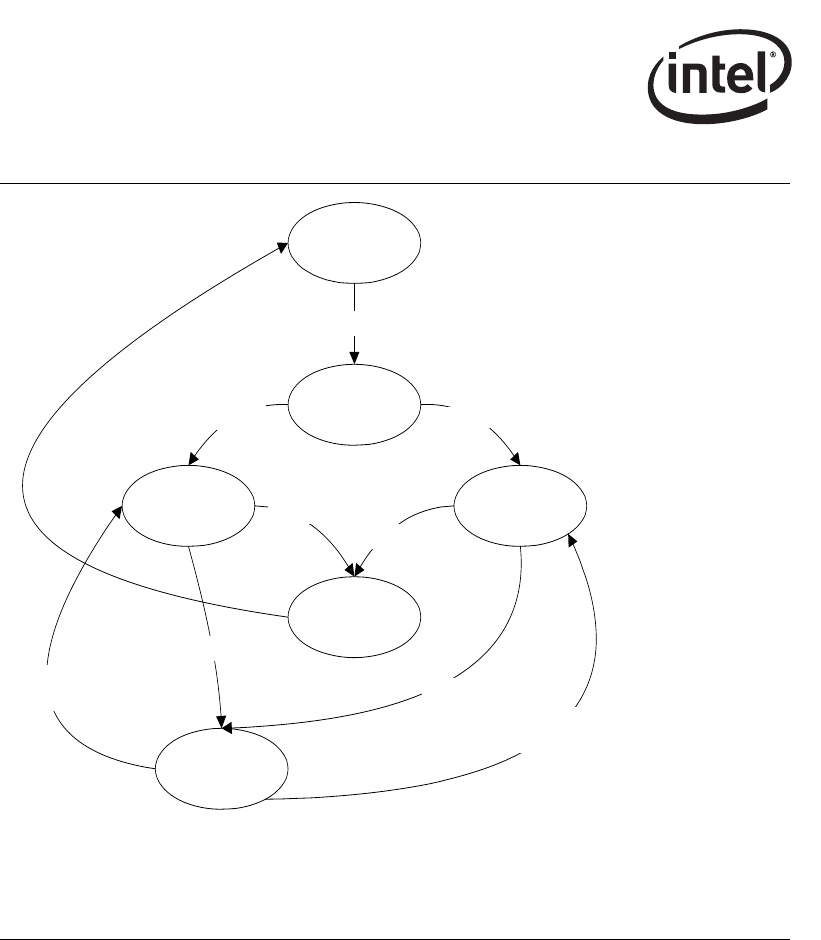

Figure 4-4. Master Write Command Usage Algorithm

4.3.1.1 MWI Bursts

•

If there is at least one cache line of data remaining, then the Ethernet controller continues the

MWI burst.

• If there is not at least one cache line of data remaining, then the Ethernet controller terminates

the transaction on the boundary, re-acquires the bus, and issues a MW command for the

remainder of data.

• If the transaction is terminated prematurely due to a target disconnect or latency time-out, the

Ethernet controller re-evaluates command usage based on the new start address and the

amount of remaining data.

!Aligned || (Aligned && (Count < CLS)) || !MWI_Enable

IDLE

Write Command

Determination

MW

Burst

MWI

Burst*

Terminate

Transaction

MWI

Boundary

Evaluation

Boundary || Terminate

Aligned && (Count >= CLS)

Cnt_Rmn = 0

Cnt_Rmn = 0

!MWI_Enable ||

(!Aligned || Cnt_Rmn < CLS)

MWI_Enable &&

d && Cnt_Rmn >= CLS)

Cnt_Rmn

= Remaining data for XFR

CLS

= Cache line size

Boundary

= At cache line boundary?

Aligned

= Address aligned to cache line boundary

Count

= Amount of data for XFR

Wr_Req || (Cnt_Rmn != 0)

Wr_Req

= Initial request for master write

* Either the initiation or continuation of the MWI Burst

Terminate

Terminate

= Target disconnect or latency timer ex