318 Software Developer’s Manual

Register Descriptions

13.4.40 Transmit Descriptor Tail

TDT (03818h; R/W)

This register contains the tail pointer for the transmit descriptor ring. It holds a value that is an

offset from the base, and indicates the location beyond the last descriptor hardware can process.

This is the location where software writes the first new descriptor. It points to a 16-byte datum.

Software writes the tail pointer to add more descriptors to the transmit ready queue. Hardware

attempts to transmit all packets referenced by descriptors between head and tail.

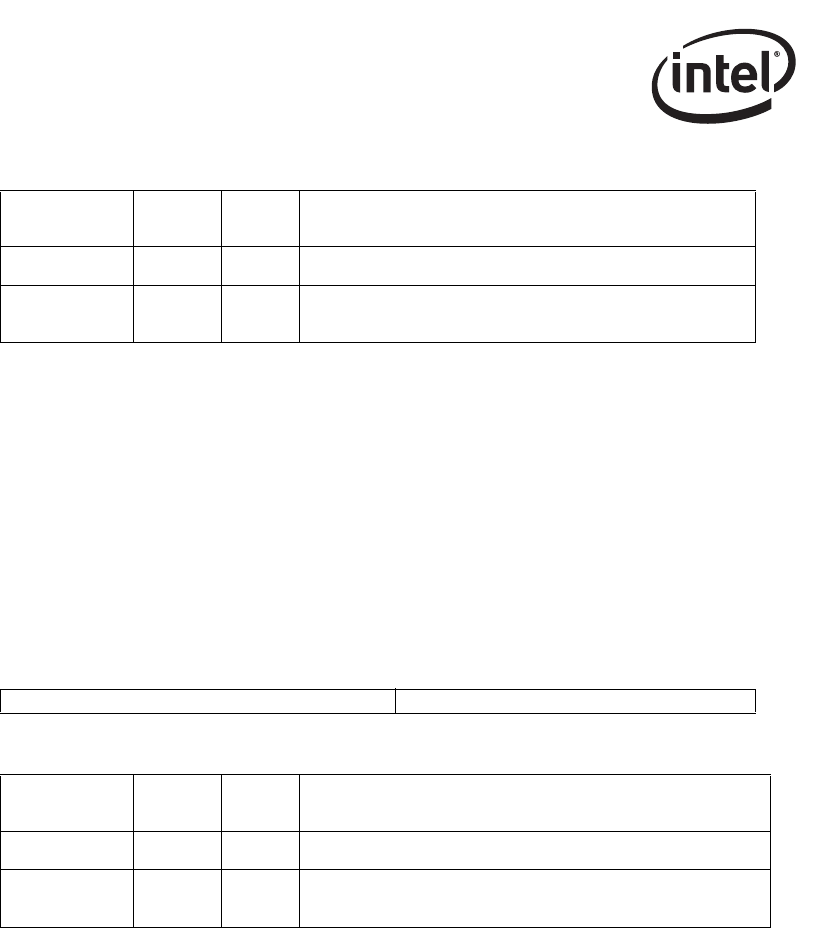

Table 13-83. TDT Register Bit Description

13.4.41 Transmit Interrupt Delay Value

TIDV (03820h; R/W)

This register contains the transmit interrupt delay value. It determines the amount of time that

elapses between writing back a descriptor that has Report Status (RS) [or Report Packet Sent (RPS)

for the 82544GC/EI] and Interrupt Delay Enable (IDE) set in the transmit descriptor and when the

IMS.TXDW (Transmit Descriptor Written Back) interrupt bit is set. Counts are in units of 1.024

s. A value of 0b is not allowed. The TIDV value is used to force timely write–back of descriptors

as well. The first packet after timer initialization starts the timer. Timer expiration flushes any

accumulated descriptors and sets an interrupt event (TXDW).

Field Bit(s)

Initial

Value

Description

TDH 15:0 0b Transmit Descriptor Head

Reserved 31:16 0b

Reserved

Reads as 0b. Should be written with 0b for future compatibility.

31 16 15 0

Reserved TDT

Field Bit(s)

Initial

Value

Description

TDT 15:0 0b Transmit Descriptor Tail

Reserved 31:16 0b

Reserved

Reads as 0b. Should be written to 0b for future compatibility.