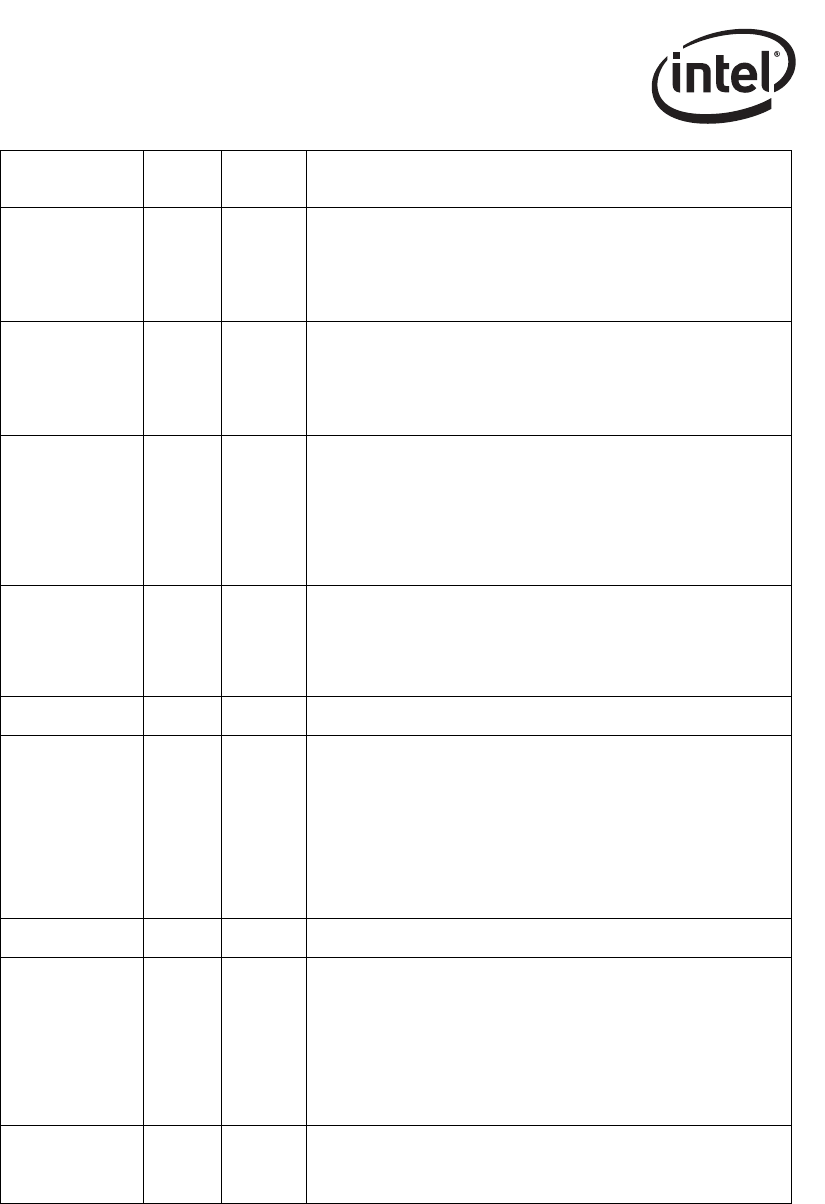

238 Software Developer’s Manual

Register Descriptions

SDP6_IODIR

SDP2_IODIR

(82541xx and

82547GI/EI)

10 0b

1

SDP6[2] Pin Directionality. Controls whether software-controllable

pin SDP6[2] is configured as an input or output (0b = input, 1b =

output). Initial value is EEPROM-configurable. This bit is not

affected by software or system reset, only by initial power-on or

direct software writes.

SDP7_IODIR

SDP2_IODIR

(82541xx and

82547GI/EI)

11 0b

1

SDP7[2] Pin Directionality. Controls whether software-controllable

pin SDP7[2] is configured as an input or output (0b = input, 1b =

output). Initial value is EEPROM-configurable. This bit is not

affected by software or system reset, only by initial power-on or

direct software writes.

ASDCHK 12 0b

ASD Check

Initiate an Auto-Speed-Detection (ASD) sequence to sense the

frequency of the PHY receive clock. The results are reflected in

STATUS.ASDV. This bit is self-clearing.

This functionality is provided for diagnostic purposes, regardless of

whether the Auto Speed Detection feature is enabled. This bit is

applicable only for internal PHY mode of operation.

EE_RST 13 0b

EEPROM Reset

When set, initiates a reset-like event to the EEPROM function. This

causes the EEPROM to be read as if a RST# assertion had

occurred. All device functions should be disabled prior to setting

this bit. This bit is self-clearing.

Reserved 14 0b

1

Reserved. Should be set to 0b.

SPD_BYPS 15 0b

Speed Select Bypass

When set to 1b, all speed detection mechanisms are bypassed,

and the Ethernet controller is immediately set to the speed

indicated by CTRL.SPEED. This can be used to override the

hardware clock switching circuitry and give full control to software.

SPD_BYPS differs from the CTRL.FRCSPD function in that

FRCSPD uses the internal clock switching circuitry rather than an

immediate forcing function of the speed settings, as does

SPD_BYPS.

Reserved 16 0b

1

Reserved. Should be set to 0b.

RO-DIS 17 0b

Relaxed Ordering Disabled

When set to 1b, the Ethernet controller does not request any

relaxed ordering transactions in PCI-X mode regardless of the

state of bit 1 in the PCI-X command register. When this bit is clear

and bit 1 of the PCI-X command register is set, the Ethernet

controller requests relaxed ordering transactions.

Note: This is a reserved bit for the 82540EP/EM, 82541xx, and

82547GI/EI. Set to 0b.

Reserved 20:18 0b

Reserved

Should be written with 0b to ensure future compatibility.

Reads as 0b.

Field Bit(s)

Initial

Value

Description