Software Developer’s Manual 241

Register Descriptions

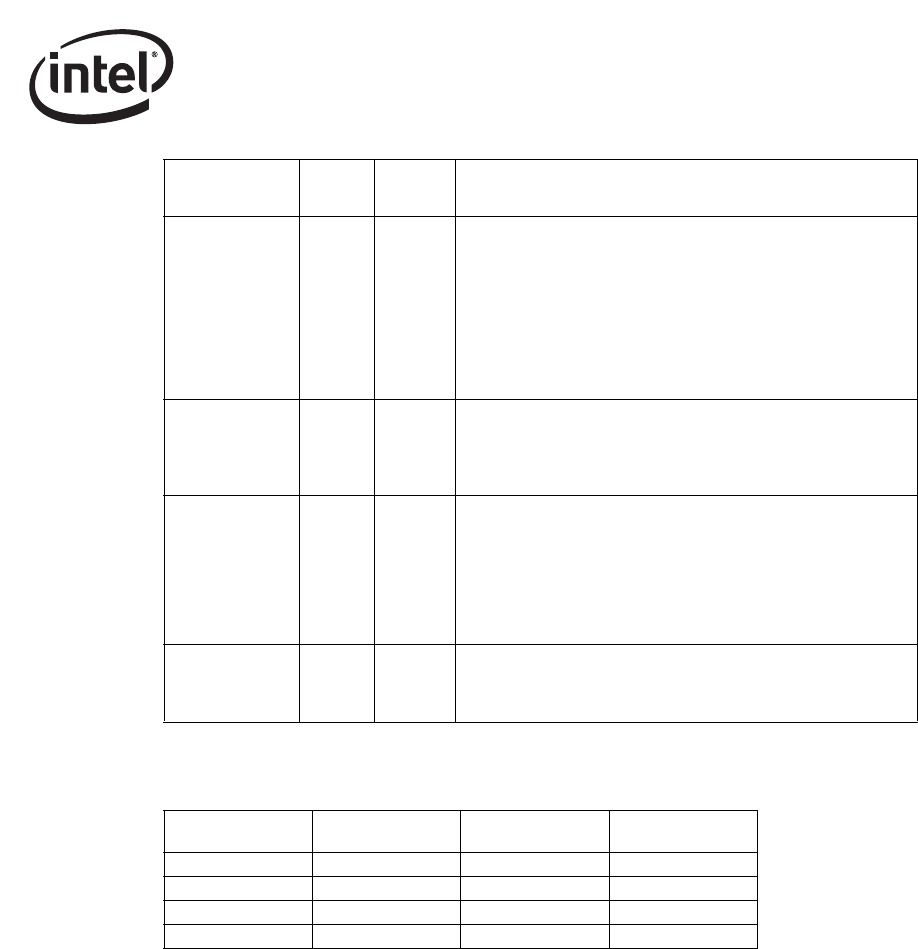

Table 13-13. 82544GC/EI GPI to SDP Bit Mapping

SPD_BYPS 15 0

Speed Select Bypass

When set to 1b, all speed detection mechanisms are bypassed,

and the Ethernet controller is immediately set to the speed

indicated by CTRL.SPEED. This might be used to override the

hardware clock switching circuitry and give full control to

software. SPD_BYPS differs from the CTRL.FRCSPD function

in that FRCSPD uses the internal clock switching circuitry rather

than an immediate forcing function of the speed settings, as

does SPD_BYPS.

IPS1 16 0

Invert Power State Bit 1

Inverts the polarity of bit 1 of the PWR_STATE signal when set

to 1b.

Configurable through the EEPROM.

RO-DIS 17 0

Relaxed Ordering Disabled

When set to 1b, the Ethernet controller does not request any

relaxed ordering transactions in PCI-X mode regardless of the

state of bit 1 in the PCI-X command register. When this bit is

clear and bit 1 of the PCI-X command register is set, the

Ethernet controller requests relaxed ordering transactions as

described.

Reserved 31:18 0

Reserved

Should be written with 0b to ensure future compatibility.

Reads as 0b.

Field Bit(s)

Initial

Value

Description

B_SDP

CTRL_EXT

(SWDPINHI)

CTRL_EXT

(GPI_EN)

ICR

(GPI)

77314

66213

5 Reserved Reserved Reserved

44011