346 Software Developer’s Manual

Register Descriptions

13.7.11 Defer Count

DC (04030h; R)

This register counts defer events. A defer event occurs when the transmitter cannot immediately

send a packet due to the medium being busy either because another device is transmitting, the IPG

timer has not expired, half-duplex deferral events, reception of XOFF frames, or the link is not up.

This register only increments if transmits are enabled. This counter does not increment for

streaming transmits that are deferred due to TX IPG.

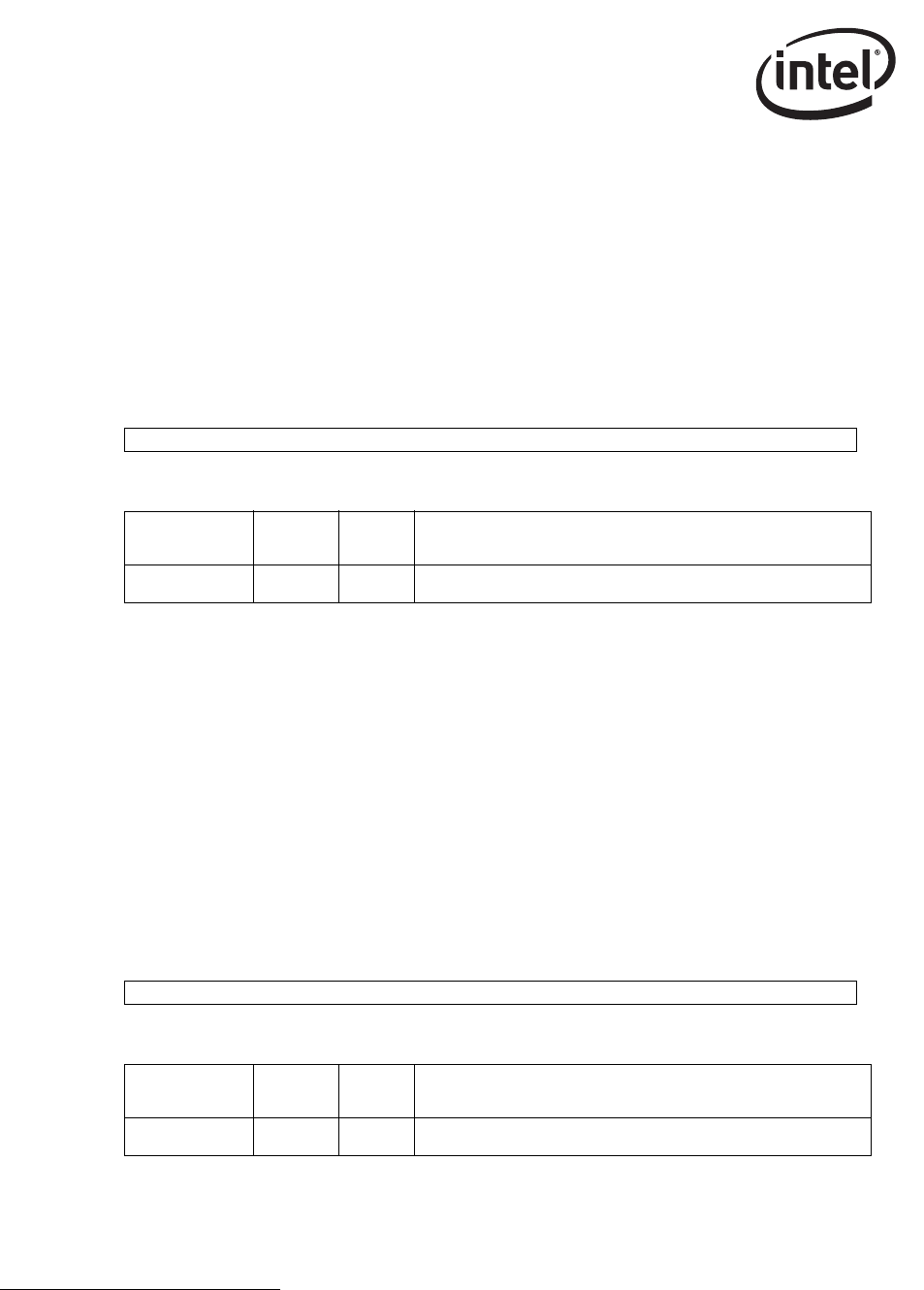

Table 13-103. DC Register Bit Description

13.7.12 Transmit with No CRS

TNCRS (04034h; R)

This register counts the number of successful packet transmissions in which the internal carrier

sense signal from the PHY was not asserted within one slot time of start of transmission.

The PHY should assert the internal carrier sense signal during every transmission. Failure to do so

may indicate that the link has failed, or the PHY has an incorrect link configuration. This register

only increments if transmits are enabled. This register is not valid in internal SerDes

1

mode (TBI

mode for the

82544GC/EI), and is only valid when the Ethernet controller is operating at full

duplex.

Table 13-104. TNCRS Register Bit Description

31 0

CDC

Field Bit(s)

Initial

Value

Description

CDC 31:0 0b Number of defer events.

1. The 82540EP/EM, 82541xx, and 82547GI/EI do not support SerDes functionality.

31 0

TNCRS

Field Bit(s)

Initial

Value

Description

TNCRS 31:0 0b Number of transmissions without a CRS assertion from the PHY.