78 Software Developer’s Manual

PCI Local Bus Interface

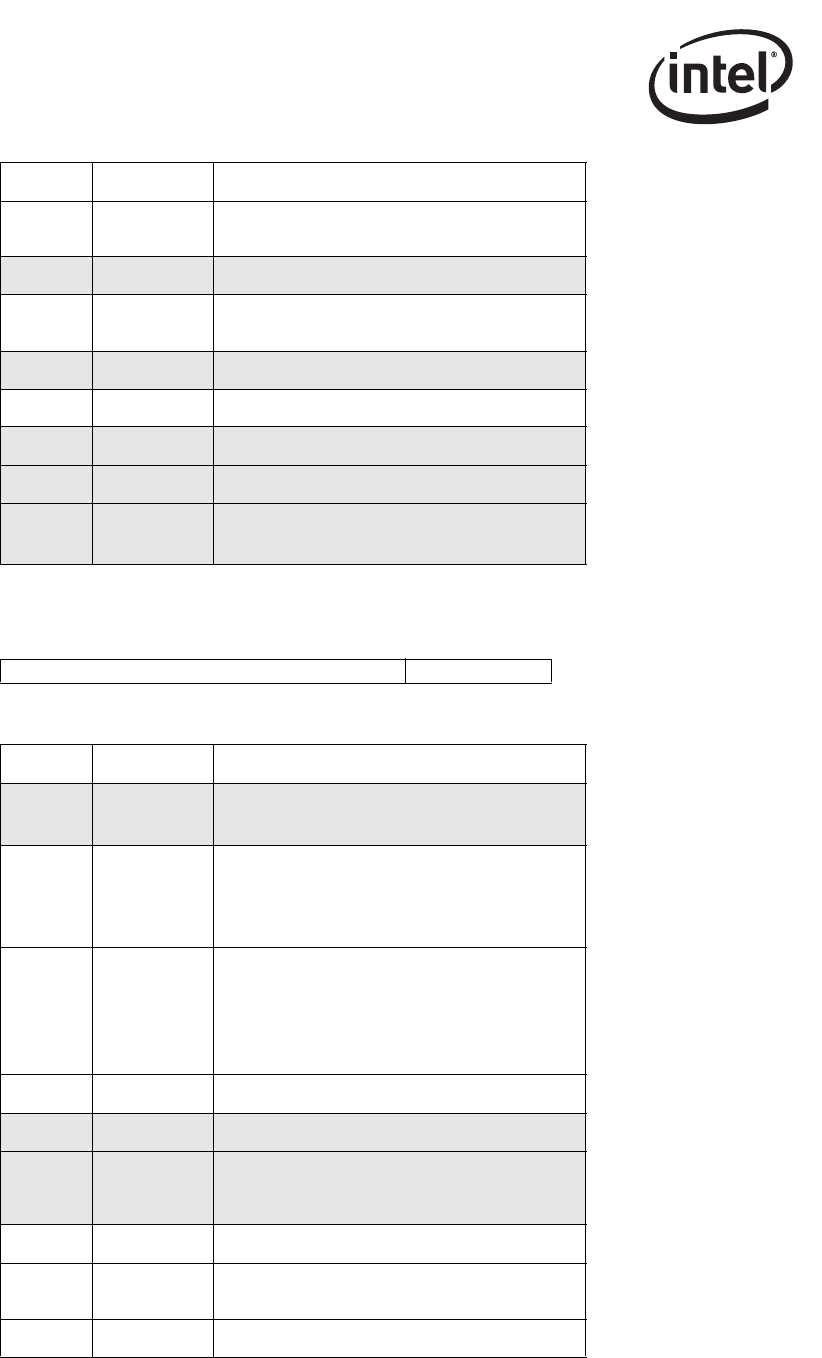

Table 4-4. Status Register Layout

40b

Memory Write and Invalidate Enable (not

applicable to the 82547GI/EI).

5 0b Palette Snoop Enable.

60b

Parity Error Response (not applicable to the

82547GI/EI).

7 0b Wait Cycle Enable.

8 0b SERR# Enable (not applicable to the 82547GI/EI).

9 0b Fast Back-to-Back Enable.

10

a

0b Interrupt Disable (INTA# or CSA signaled).

15:10

15:11

a

0b Reserved.

a. 82541xx and 82547GI/EI only.

Bit(s) Initial Value Description

15 4 3 0

Status Bits Reserved

Bit(s) Initial Value Description

3:0

2:0

a

0b Reserved.

3

a

0b

Interrupt Status. This bit is 1b when the Ethernet

controller is generating an interrupt internally.

When Interrupt Disable in the Command Register

is also cleared, the Ethernet controller asserts

INTA# or signal an interrupt over CSA.

41b

New Capabilities: Indicates that an Ethernet

controller implements Extended Capabilities. The

Ethernet controller sets this bit and implements a

capabilities list to indicate that it supports PCI

Power Management, PCI-X Bus, and message

signaled interrupts.

5 1b 66 MHz Capable (don’t care for the 82547GI/EI).

6 0b UDF Supported. Hardwired to 0b for PCI 2.3

a

.

7 0b

Fast Back-to-Back CapableThis bit must be

cleared to 0b in PCI-X mode (not applicable to the

82547GI/EI).

8 0b Data Parity Reported.

10:9 01b

DEVSEL Timing (indicates medium device). Not

applicable to the 82547GI/EI.

11 0b Signaled Target Abort.