Software Developer’s Manual 271

Register Descriptions

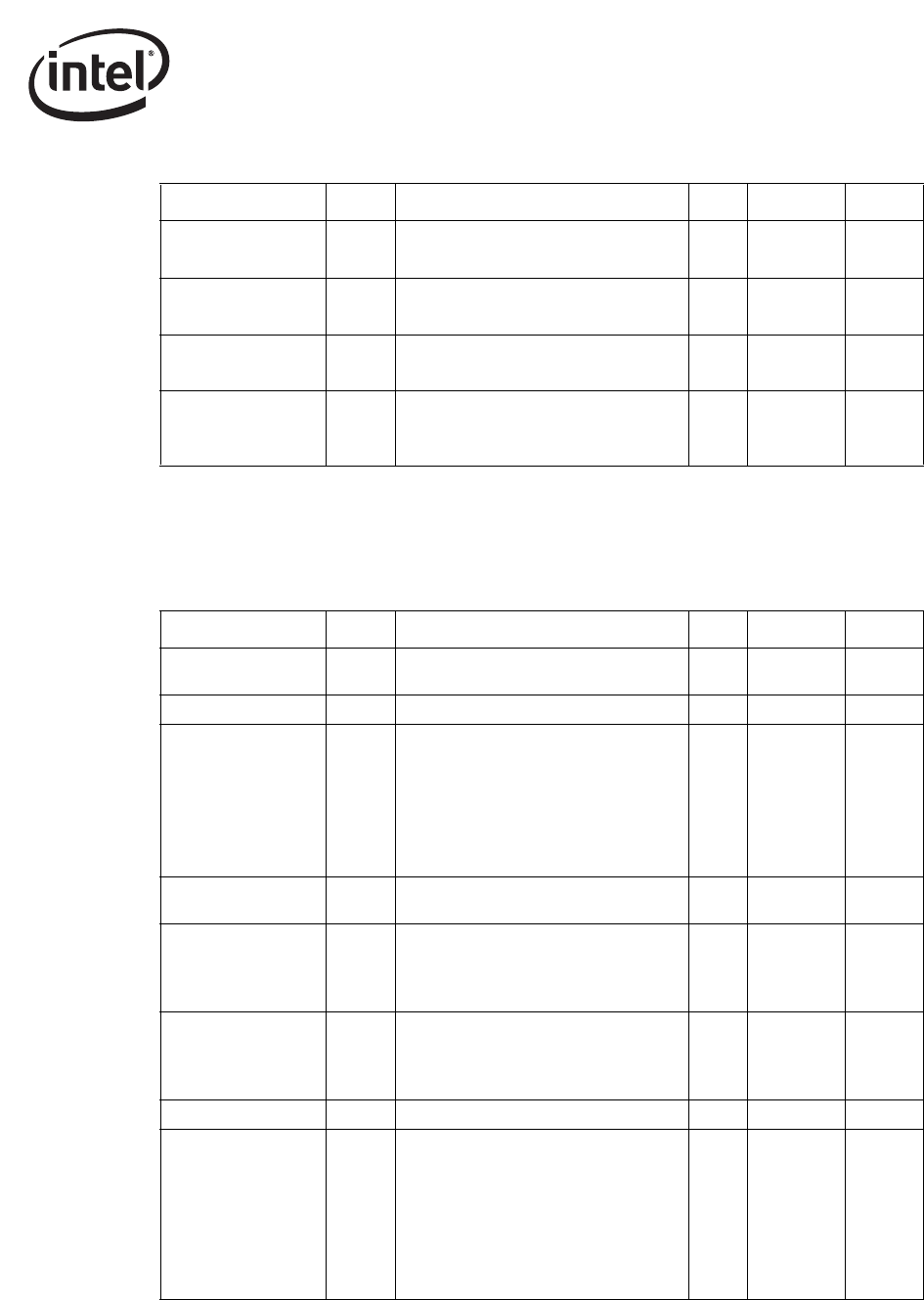

PHY Port Control Register (82541xx and 82547GI/EI Only)

PPCONT (18d; R/W)

Page Received

Interrupt Enable

12

1b = Interrupt enable.

0b = Interrupt disable.

R/W 0b Retain

Duplex Changed

Interrupt Enable

13

1b = Interrupt enable.

0b = Interrupt disable.

R/W 0b Retain

Speed Changed

Interrupt Enable

14

1b = Interrupt enable.

0b = Interrupt disable.

R/W 0b Retain

Auto-Negotiation

Error

Interrupt Enable

15

1b = Interrupt enable.

0b = Interrupt disable.

R/W 0b Retain

Table 13-36. PHY Port Control Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 3:0

Always read as 0b. Write to 0b for

normal operation.

R/W 0b 0b

TP Loopback 4 Allow gigabit loopback on twisted pairs. R/W 0b 0b

Fast Downshift

Enable

5

82541EI/82547GI (B0 stepping):

Reserved, write to 0b.

82541/GI/ER and 82547GI (B1

stepping): Fast 1000 Mb to 100 Mb

downshift enable.

0b = Downshift after 16 seconds.

1b = Downshift after 10 seconds.

R/W 0b 0b

Reserved 8:6

Always read as 0b. Write to 0b for

normal operation.

R/W 0b 0b

Non-Compliant

Scrambler

Compensation

9

1b = Detect and correct for non-

compliant scrambler.

0b = Detect and report non-compliant

scrambler.

R/W 0b 0b

1

TEN_CRS_Select 10

1b = Extend CRS to cover GMII latency

and RX_DV.

0b = Do not extend CRS (RX_DV can

continue past CRS).

R/W 1b 1b

Reserved 11 Always write as 1b for normal operation. R/W 1b 1b

Auto-MDI-X 12

Auto-MDI-X algorithm enable.

1b = Enable Auto-MDI-X mode.

0b = Disable Auto-MDI-X mode (manual

mode).

Note: When forcing speed to 10Base-T

or 100Base-T, use manual mode. Clear

the bit and set PHY register 18, bit 13

according to the required MDI-X mode.

R/W 1b 1b

Table 13-35. PHY Interrupt Enable Bit Description

Field Bit(s) Description Mode HW Rst SW Rst