Software Developer’s Manual 277

Register Descriptions

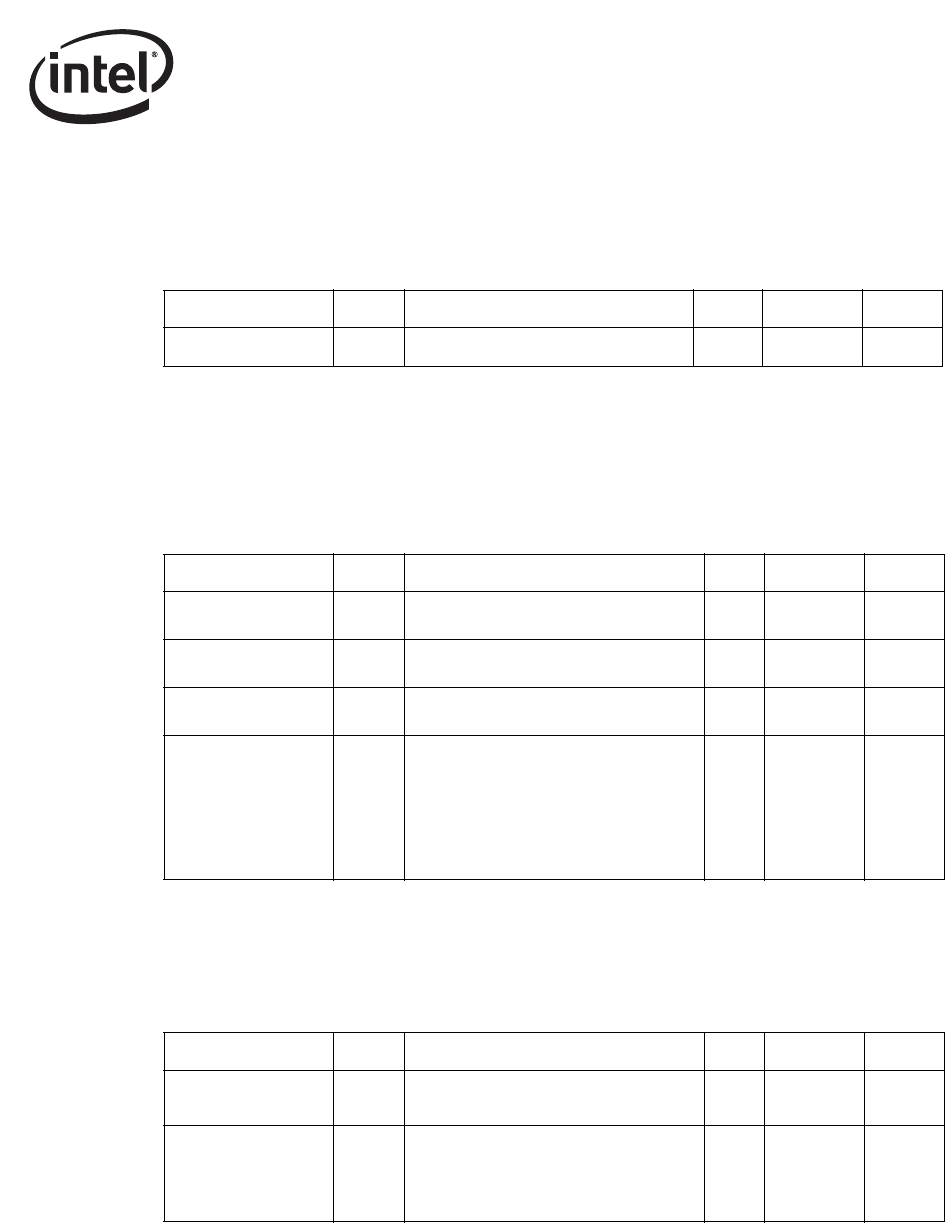

13.4.7.1.18 PHY Receive Error Counter

PREC (21d; R)

NOTE: The counter stops at FFFFh and does not roll over.

PHY Channel Quality Register (82541xx and 82547GI/EI Only)

PCHAN (21d; R)

13.4.7.1.19 SPEED_TEN_LED and LINK_ACT_LED Control (82541xx and 82547GI/EI Only)

(23d; R/W)

Table 13-41. PHY Receive Error Counter Bit Description

Field Bit(s) Description Mode HW Rst SW RST

Receive Error Count 15:0 Error Count. RO,SC 0000h 0000h

Table 13-42. PHY Channel Quality Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

MSE D 3:0

The converged mean square error for

Channel D.

RO 0b 0b

MSE C 7:4

The converged mean square error for

Channel C.

RO 0b 0b

MSE B 11:8

The converged mean square error for

Channel B.

RO 0b 0b

MSE A 15:12

The converged mean square error for

Channel A. This field is only meaningful

in gigabit, or in 100BASE-TX if this is

the receive pair.

Use of this field is complex and needs

interpretation based on the chosen

threshold value.

RO 0b 0b

Table 13-43. SPEED_TEN_LED and LINK_ACT_LED Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

LED Source Select 3:0

MUX the designated input to

SPEED_TEN_LED.

R/W 0000b 0000b

LED Blink Disable 4

Disable the SPEED_TEN_LED Blink

Logic.

0b = Enable logic.

1b = Disable logic.

R/W 0b 0b