80 Software Developer’s Manual

PCI Local Bus Interface

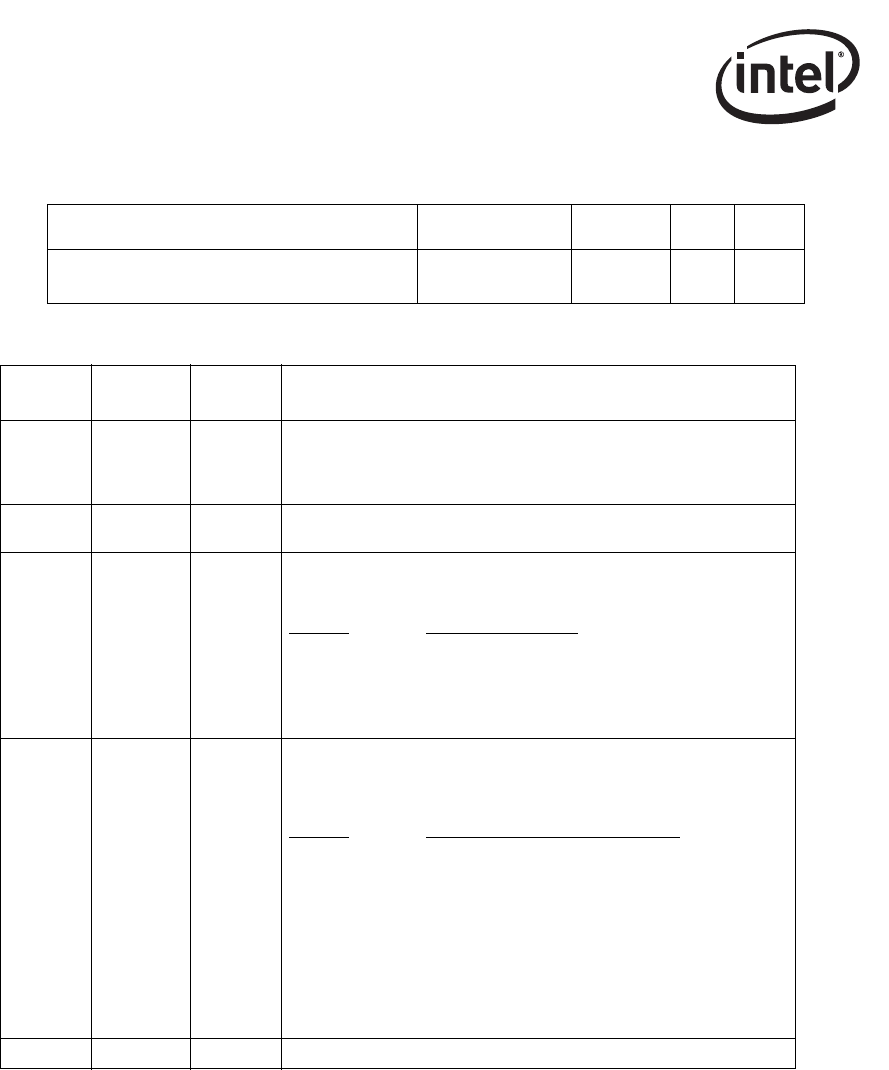

4.1.1.3 PCI-X Command

15 7 6 4 3 2 1 0

Reserved

Max. Split Trans-

actions

Read

Count

RO DP

Bits

Read

Write

Initial

Value

Description

0RW0b

Data Parity Error Recovery Enable. If this bit is 1b, the Ethernet

controller attempts to recover from Parity errors. If this bit is 0b, the

Ethernet controller asserts SERR# (if enabled) whenever the Master

Data Parity Error bit (Status Register, bit 8) is set.

1RW1b

Enable Relaxed Ordering. If this bit is set, the Ethernet controller sets

the Relaxed Ordering attribute bit in some transactions.

3:2 RW 0b

Maximum Memory Read Byte Count. This register sets the

maximum byte count the Ethernet controller uses for a Memory Read

Sequence. The allowable values are:

Register

Maximum Byte Count

0 512

1 1024

2 2048

3 4096

6:4 RW 0b

Maximum Outstanding Split Transactions. This register sets the

maximum number of outstanding split transactions that the Ethernet

controller uses. The Ethernet controller is only allowed to have one

outstanding split transaction at any time.

Register

Maximum Outstanding Transactions

01

1 2

23

34

4 8

5 12

6 16

7 32

15:7 R 0b Reserved. Reads as 0b