10 Software Developer’s Manual

Architectural Overview

2.3 Microarchitecture

Compared to its predecessors, the PCI/PCI-X Family of Gigabit Ethernet Controller’s MAC adds

improved receive-packet filtering to support SMBus-based manageability, as well as the ability to

transmit SMBus-based manageability packets. In addition, an ASF-compliant TCO controller is

integrated into the controller’s MAC for reduced-cost basic ASF manageability.

Note: The 82544GC/EI and 82541ER do not support SMBus-based manageability.

For the 82546GB/EB, this new functionality is packaged in an integrated dual-port combination.

The architecture includes two instances of both the MAC and PHY along with a single PCI/PCI-X

interface. As a result, each of the logical LAN devices appear as a distinct PCI/PCI-X bus device.

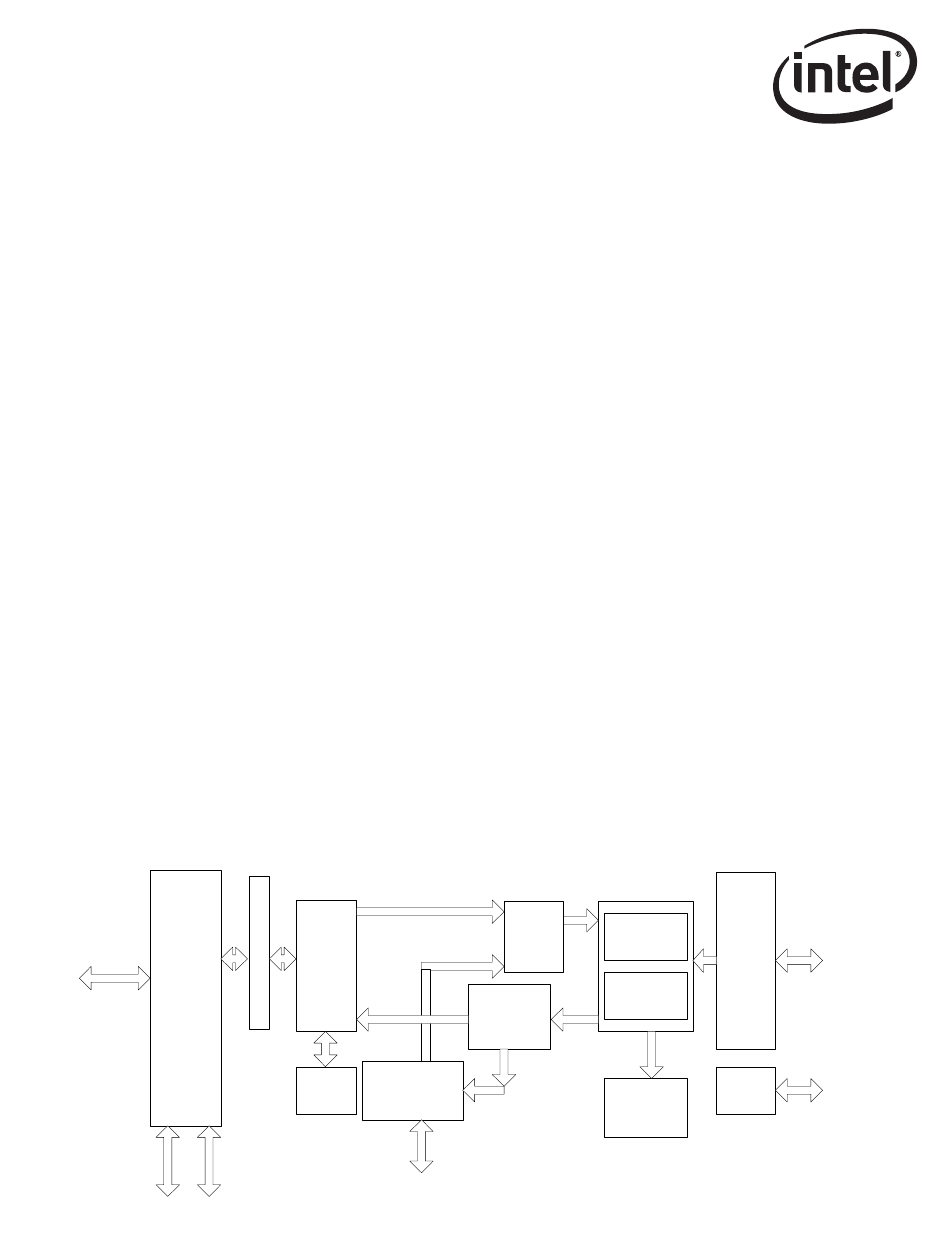

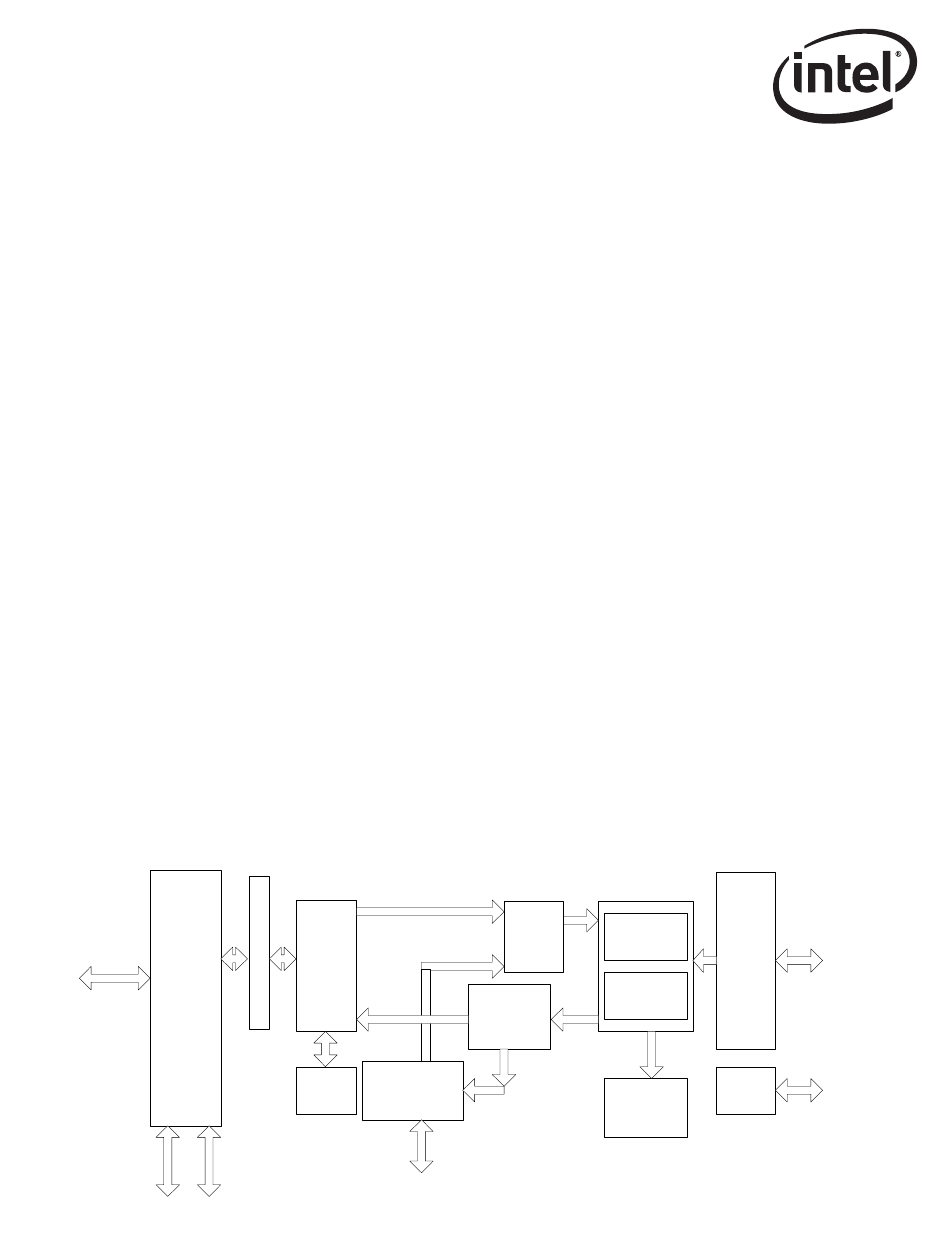

The following sections describe the hardware building blocks. Figure 2-4 shows the internal

microarchitecture.

2.3.1 PCI/PCI-X Core Interface

The PCI/PCI-X core provides a complete glueless interface to a 33/66 MHz, 32/64-bit PCI bus or a

33/66/133 MHz, 32/64 bit PCI-X bus. It is compliant with the PCI Bus Specification Rev 2.2 or 2.3

and the PCI-X Specification Rev. 1.0a. The Ethernet controllers provide 32 or 64 bits of addressing

and data, and the complete control interface to operate on a 32-bit or 64-bit PCI or PCI-X bus. In

systems with a dedicated bus for the Ethernet controller, this provides sufficient bandwidth to

support sustained 1000 Mb/s full-duplex transfer rates. Systems with a shared bus (especially the

32-bit wide interface) might not be able to maintain 1000 Mb/s, but can sustain multiple hundreds

of Mbps.

Figure 2-4. Internal Architecture Block Diagram

PCI/

PCI-X

Core

PCI Interface

EEPROM Flash

DMA

Engine

Packet

Buffer

TX MAC

(10/100/

1000 Mb)

RX MAC

(10/100/

1000 Mb)

Packet/

Manageability

Filter

TX

Switch

ASF

Manageability

GMII/

MII

Link I/F

MDIO

MDIO

RMON

Statistics

SM Bus

Host Arbiter