Software Developer’s Manual 265

Register Descriptions

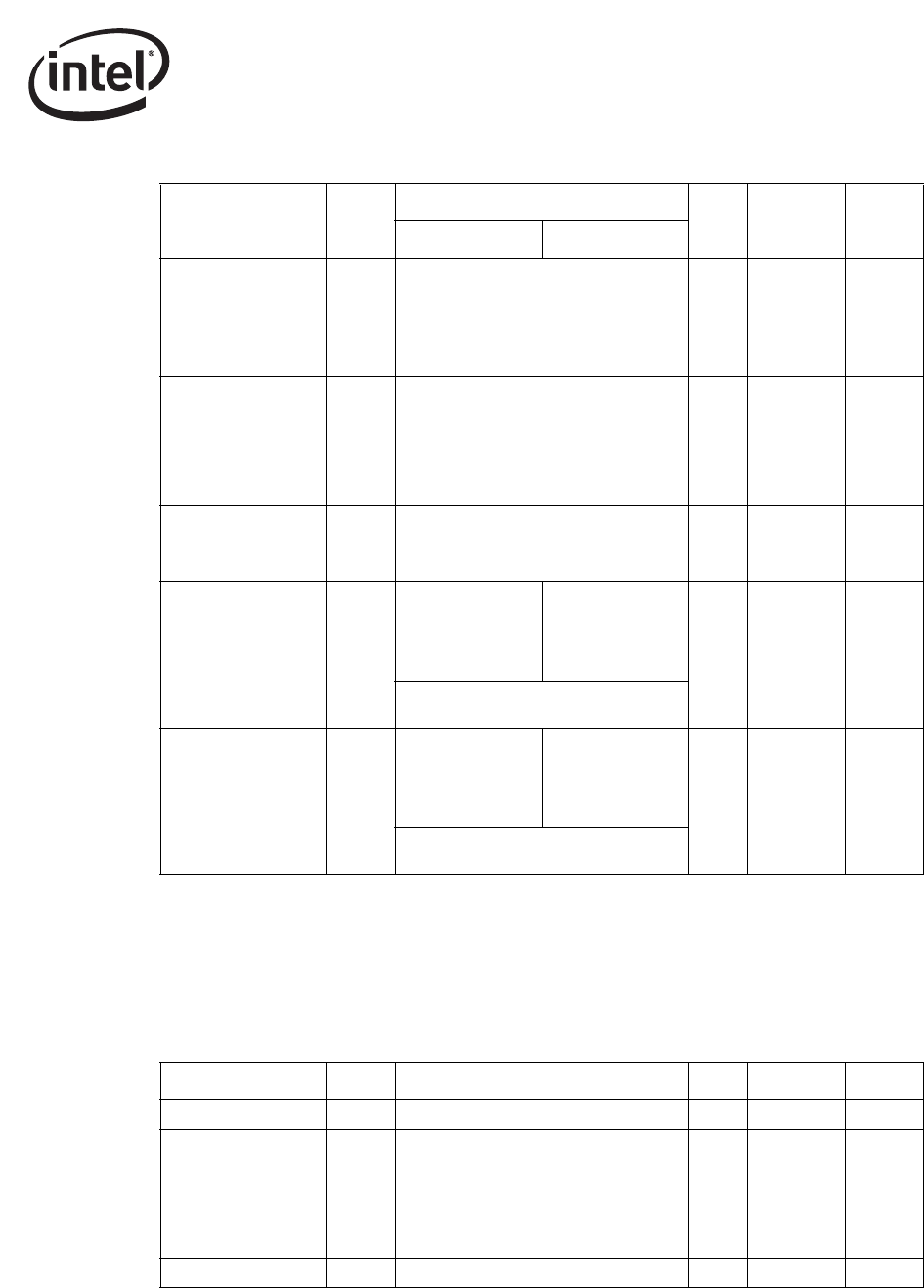

PHY Port Configuration Register (82541xx and 82547GI/EI Only)

PPCONF (16d; R/W)

Energy Detect 9:8

Energy Detect.

0xb = Off.

10b = Sense only on receive.

11b = Sense and periodically transmit

NLP.

R/W 0b Retain

Force Link Good 10

1b = Force link good.

0 b = Normal operation.

If link is forced to be good, the link state

machine is bypassed and the link is

always up. In 1000BASE-T mode this

has no effect.

R/W 0b Retain

Assert CRS on

Transmit

11

1b = Assert on transmit.

0b = Never assert on transmit.

This bit has no effect in full duplex.

R/W 0b Retain

Receive FIFO depth 13:12

00b = 16 Bits

01b = 24 Bits

10b = 32 Bits

11b = 40 Bits

00b = 8 Bits

01b = 12 Bits

10b = 16 Bits

11b = 20 Bits

R/W 00b Retain

Receive FIFO is enabled in internal

SerDes mode

2

or serial interface mode.

Transmit FIFO depth 15:14

00b = 16 Bits

01b = 24 Bits

10b = 32 Bits

11b = 40 Bits

00 b= 8 Bits

01b = 12 Bits

10b = 16 Bits

11b = 20 Bits

R/W 00b Retain

Transmit FIFO is enabled in 1000BASE-

T mode or serial interface mode.

1. 82544GC/EI only.

2. TBI Mode for the 82544GC/EI.

Table 13-32. PHY Port Configuration Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 0 Write to 0b for normal operation. R/W 0b 0b

Alternate NP Feature 1

1b = Enable alternate Auto-Negotiate

next page feature.

0b = Disable alternate Auto-Negotiate

next page feature.

If polarity is disabled, then the polarity is

forced to be normal in 10BASE-T.

R/W 0b 0b

Reserved 3:2 Write to 0b for normal operation. R/W 0b 0b

Table 13-31. PHY Specific Control Register Bit Description

Field Bit(s)

Description

Mode HW Rst SW Rst

1000BASE-T 10/100BASE-T