314 Software Developer’s Manual

Register Descriptions

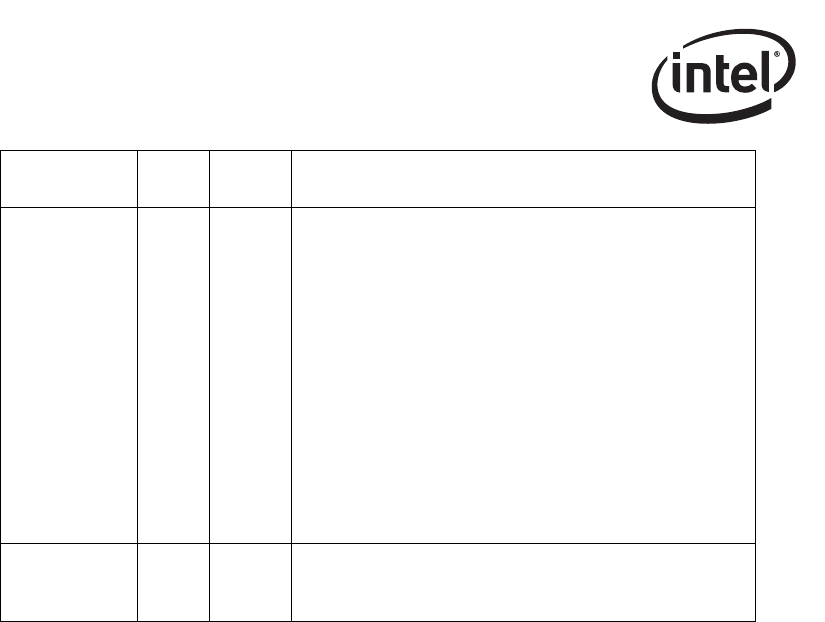

13.4.35 Adaptive IFS Throttle - AIT

AIFS (00458;R/W)

This register throttles back-to-back transmissions in the transmit packet buffer and delays their

transfer to the CSMA/CD transmit function. As a result, it can be used to delay the transmission of

back-to-back packets on the wire.

For the

82544GC/EI, this register can be used to increase the IPG value between transmitting

back-to-back packets on the wire and between frames while in half-duplex mode.

IPGR2 29:20 X

IPG Receive Time 2

Specifies the total length of the IPG time for non back-to-back

transmissions.

Measured in increments of the MAC clock:

• 8 ns MAC clock when operating @ 1 Gbps (82544GC/EI

only).

• 80 ns MAC clock when operating @ 100 Mbps

• 800 ns MAC clock when operating @ 10 Mbps.

In order to calculate the actual IPG value, a value of six should

be added to the IPGR2 value as six MAC clocks are used by the

MAC for synchronization and internal engines.

For the IEEE 802.3 standard IPG value of 96-bit time, the value

that should be programmed into IPGR2 is six (total IPG delay of

12 MAC clock cycles) According to the IEEE802.3 standard,

IPGR1 should be 2/3 of IPGR2 value.

IPGR2 is significant only in half-duplex mode of operation.

Reserved 31:30 X

Reserved

Read as 0b.

Should be written with 0b for future compatibility.

Field Bit(s)

Initial

Value

Description