256 Software Developer’s Manual

Register Descriptions

82544GC/EI Only:

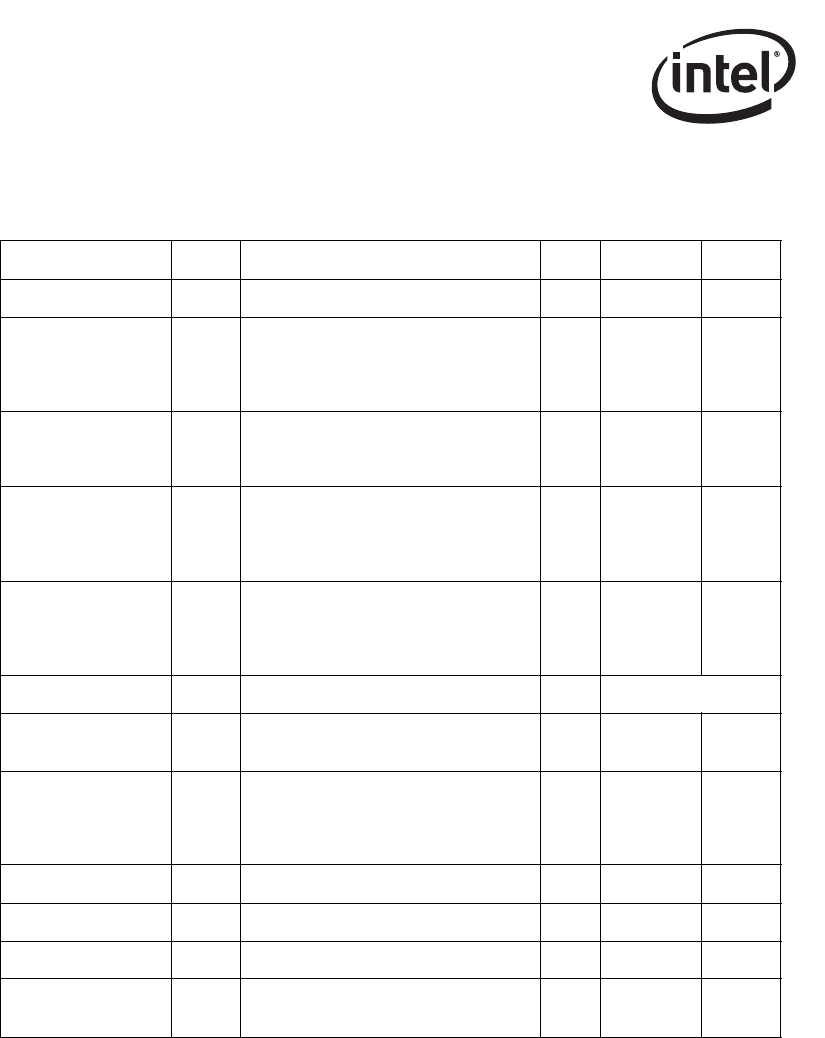

Table 13-23. Link Partner Ability Register (Base Page) Bit

Description

1

1. (MODE[3:0] is one of 001xb, 0111b).

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 4:0 Reserved. Should be set to 00000b. RO 00000b 00000b

10BASE-TX Half

Duplex

5

1b = 10 Base-TX half duplex is

available.

0b = 10 Base-TX half duplex is not

available.

RO 0b 0b

10BASE-TX Full

Duplex

6

1b = 10 Base-TX full duplex is available.

0b = 10 Base-TX full duplex is not

available.

RO 0b 0b

100BASE-TX Half

Duplex

7

1b = 100 Base-TX half duplex is

available.

0b = 100 Base-TX half duplex is not

available.

RO 0b 0b

100BASE-TX Full

Duplex

8

1b = 100 Base-TX full duplex is

available.

0b = 100 Base-TX full duplex is not

available.

RO 0b 0b

100BASE-T4 9 0b = Not capable of 100BASE-T4. RO Always 0b

Pause 10

1b = Pause operation is available.

0b = Pause operation is not available.

RO 0b 0b

Asymmetric Pause 11

1b = Asymmetric Pause operation is

available.

0b = Asymmetric Pause operation is not

available.

RO 0b 0b

Reserved 12 Reserved. Should be set to 0b. RO 0b 0b

Remote Fault 13 Indicates a remote fault. RO 0b 0b

Reserved 14 Reserved. Should be set to 0b. RO 0b 0b

Next Page 15

1b = Link partner is Next Pagable.

0b = Link partner is not Next Pagable.

RO 0b 0b