Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

February 2007 HDD

Document Number: 305261, Revision: 004 105

DDR-SDRAM—Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

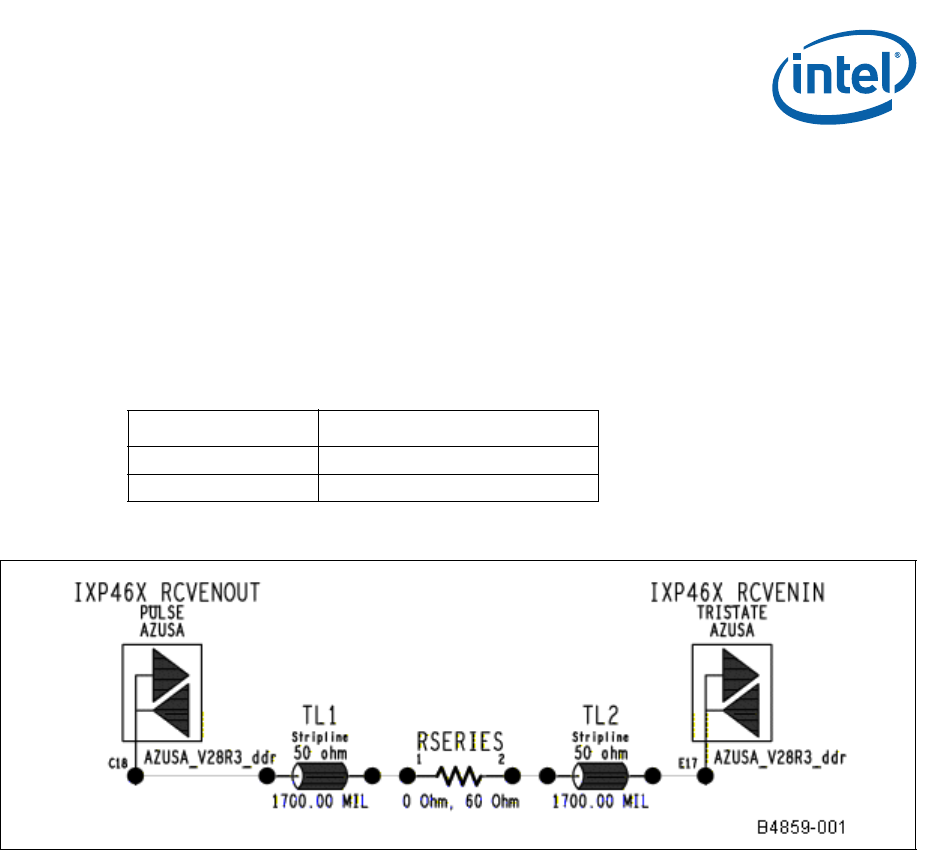

7.2.5 RCVENIN and RCVENOUT

The Receive Enable In (RCVENIN) and Receive Enable Out (RCVENOUT) should be

connected and routed to match the length of the clock signal plus the average data

signal trace. This length matching is important to insure the signal propagation delay of

RCVENIN/RCVENOUT is the same as that for the clock plus average DQ length.

Table 40 identifies the transmission line lengths for the RCVENIN/RCVENOUT topology

shown in Table 49. These lengths were chosen from the previous clock and data group

simulation topologies.

Table 40. Control Group Topology Transmission Line Characteristics

Transmission Line Length

TL1 (T

pd

= 175 ps/in) ~1,700 mils

TL2 (T

pd

= 175 ps/in) ~1,700 mils

Figure 49. DDR RCVENIN/RCVENOUT Topology