Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

February 2007 HDD

Document Number: 305261; Revision: 004 33

General Hardware Design Considerations—Intel

®

IXP45X and Intel

®

IXP46X Product Line of

Network Processors

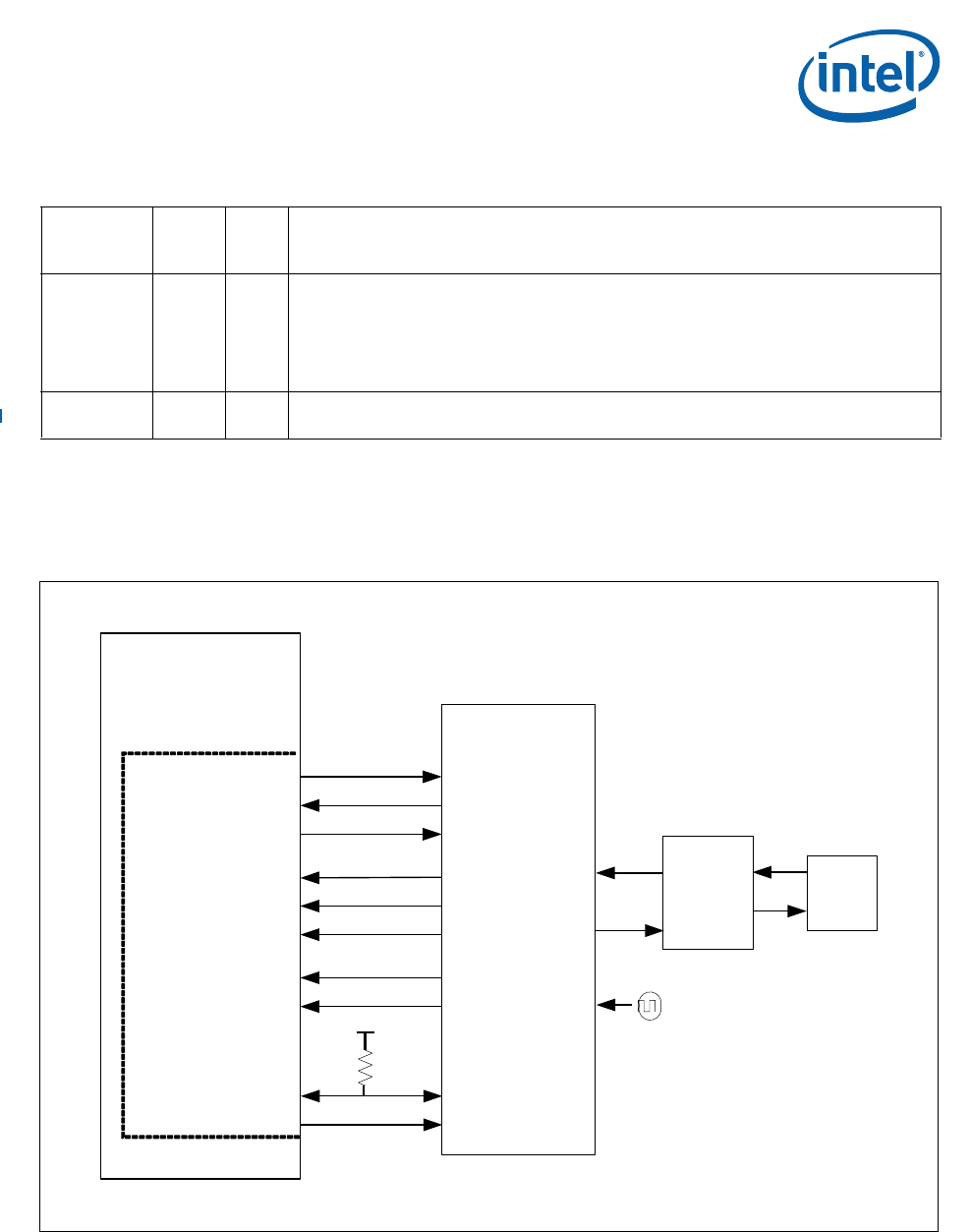

3.5.2 Device Connection, MII

Figure 8 is a typical example of an Ethernet PHY device interfacing to one of the MACs

via the MII hardware protocol.

Table 11. MAC Management Signal Recommendations NPE A,B,C

Name

Input/

Output

Pull

Up/

Down

Recommendations

ETH_mdio I/O Yes

NPE A,B,C

Management data output.

An external pull-up resistor of 1.5 KΩ is required on ETH_MDIO to properly quantify the

external PHYs used in the system. For specific implementation, see the IEEE 802.3

specification.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

ETH_mdc I/O No

NPE A,B,C

Management data clock.

Figure 8. MII Interface Example

Intel

®

IXP46X

Product Line of

Network Processors

MII Interface

ETH_RXDATA[3:0]

ETH_TXDATA[3:0]

ETH_TXCLK

ETH_RXDV

ETH_COL

ETH_MDIO

ETH_MDC

Magnetics RJ45

25 MHz

ETH_RXCLK

ETH_CRS

ETH_TXEN

RXDATA[3:0]

TXDATA[3:0]

TXCLK

RXDV

COL

MDIO

MDC

RXCLK

TXEN

10/100

PHY

CRS

VCC (3.3 V)

B4101-003

1.5 KΩ