Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors—General Hardware

Design Considerations

Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

HDD February 2007

30 Document Number: 305261; Revision: 004

3.5 MII/SMII Interface

The IXP45X/IXP46X network processors support a maximum of three Ethernet MACs.

Depending on the IXP45X/IXP46X network processors part number used, various

combinations can be used. For the various features that can be enable a variety of

needs, see the Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

Datasheet.

All MACs contained in the NPEs are compliant to the IEEE 802.3 specification and

handle flow control for the IEEE 802.3Q VLAN specification.

The Management Data Interface (MDI) supports a maximum of 32 PHY addresses. MDI

signals are required to be connected to every PHY chip. Each PHY port is assign a

unique address in the external PHY chip from 0 to 31, totaling a maximum of 32 PHY

addresses. The maximum number of MACs supported by the IXP45X/IXP46X network

processors is three.

The MII interface supports clock rates of 25 MHz for 100-Mbps operation or 2.5 MHz for

10-Mbps operation.

SMII interface supports clock rate of 125 MHz for 10/100-Mbps operation.

General PHY Ethernet devices routing guidelines can be found in Section 5.2.3, “SMII

Signal Considerations” on page 67. For more detailed information, see the IEEE 802.3

specification.

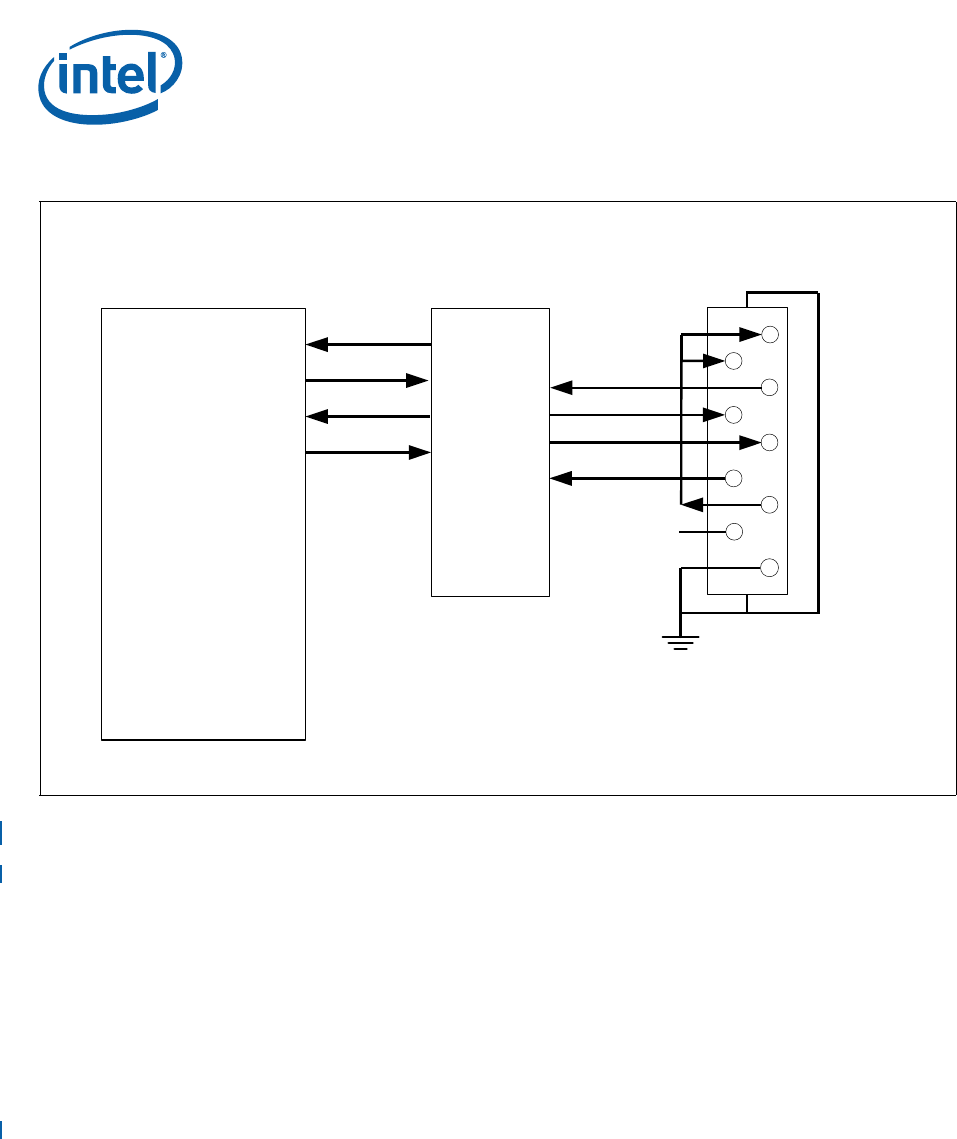

Figure 7. UART Interface Example

Intel

®

IXP46X

Product Line of

Network Processors

Intel

®

IXP46X

Product Line of

Network Processors

UART

Interface

DB9

Connector

CTS1_N

RTS1_N

RXDATA1

TXDATA1

OUT4

OUT1

RS-232

Transceiver

IN3

IN2

NC

IN1

IN4

OUT2

OUT3

1 DCD

2 RX

3 TX

4 DTR

5 GND

6 DSR

7 RTS

8 CTS

9 RI

1

6

2

7

3

8

4

9

5

B4099-003