1999 May 10 26

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) CODEC UDA1325

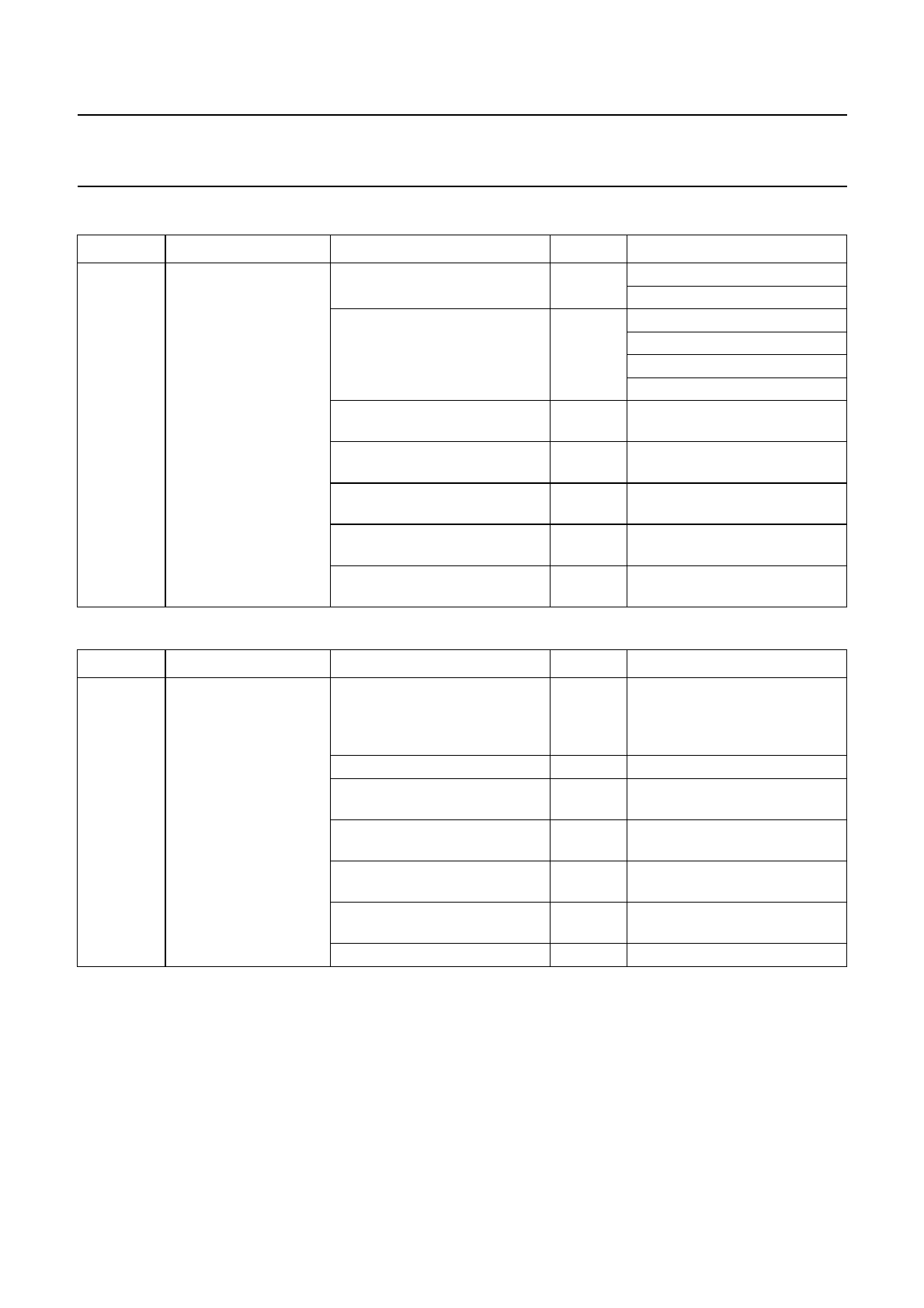

Table 19 Clock shop register

Table 20 Reset control and APLL register

ADDRESS REGISTER COMMENTS BIT VALUE

1000h clock shop settings selection ADC clock source 7 0 = ADC clock from APLL

1 = ADC clock from OSCAD

divide factor Q 6 and 5 00 = ADC clock divided-by-1

01 = ADC clock divided-by-2

10 = ADC clock divided-by-4

11 = ADC clock divided-by-8

clock ADAC 4 0 = enable

1 = disable

clock 48 MHz internal 3 0 = enable

1 = disable

clock recovered by PSIE 2 0 = enable

1 = disable

ADC clock 1 0 = enable

1 = disable

OSCAD oscillator 0 0 = power on

1 = power off

ADDRESS REGISTER COMMENTS BIT VALUE

1001h reset control and APLL

settings

fcode (1 and 0)

clock frequency selection APLL

7 and 6 00 = 256 × 44.1 kHz

01 = 256 × 32 kHz

10 = 256 × 48 kHz

11 = 256 × 44.1 kHz

reserved 5 X

reset ADAC 4 0 = reset off

1 = reset on

reset MMU 3 0 = reset off

1 = reset on

reset digital I/O-interface 2 0 = reset off

1 = reset on

reset ADIF 1 0 = reset off

1 = reset on

reserved 0 X