1999 May 10 5

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) CODEC UDA1325

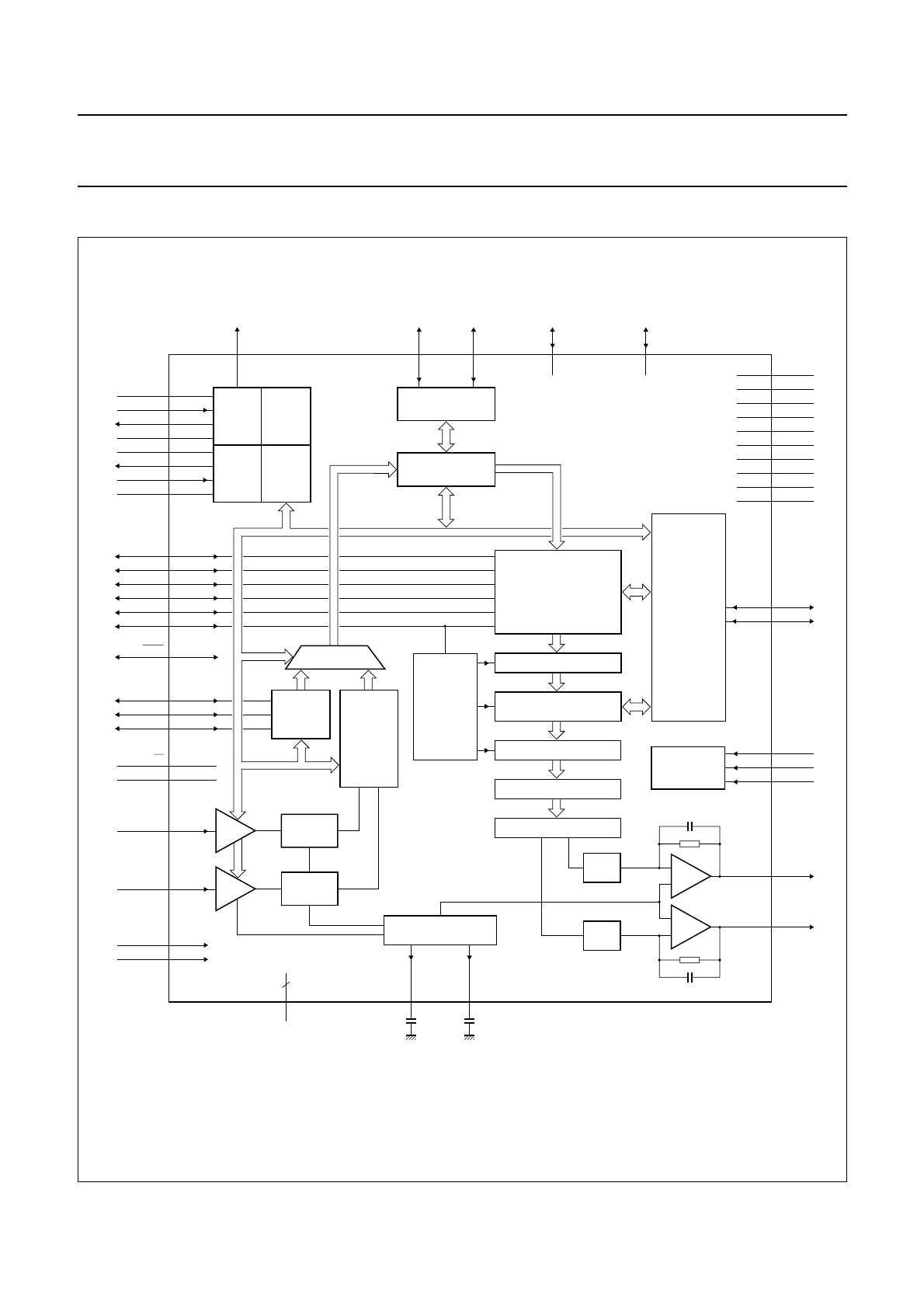

BLOCK DIAGRAM

Fig.1 Block diagram (QFP64 package).

handbook, full pagewidth

MGM108

TIMING

ANALOG

PLL

OSC

48 MHz

OSC

ADC

24 (19)

27

25 (20)

26 (21)

28 (22)

52 (39)

53 (40)

54 (41)

55 (42)

63 (4)

1 (5)

2 (6)

13 (14)

17 (16)

15 (15)

(12) 11

(13) 12

(10) 9

(11) 10

(23) 32

(24) 33

(29) 38

(30) 39

(33) 42

(35) 44

ANALOG FRONT-END

USB-PROCESSOR

DIGITAL I/O

FIFO

AUDIO FEATURE

PROCESSING DSP

UPSAMPLE FILTERS

VARIABLE HOLD REGISTER

3rd-ORDER NOISE SHAPER

REFERENCE VOLTAGE

57 (1)

59 (2)

61 (3)

43 (34)

47 (36)

8 (9) 6 (8)

MICRO-

CONTROLLER

TEST

CONTROL

BLOCK

SAMPLE

FREQUENCY

GENERATOR

MUX

I

2

S-BUS

INTERFACE

DECIMATOR

FILTER

PGA

LEFT

Σ∆ ADC

PGA

RIGHT

Σ∆ ADC

LEFT

DAC

RIGHT

DAC

49 (37)

51 (38)

45, 46 41 (32) 40 (31)

V

ref(AD)

V

ref(DA)

(28) 37

(25) 34

(27) 36

(26) 35

(7) 4

(18) 21

(17) 19

n.c.

UDA1325

+

−

−

+

VRN

VINR

V

SSA2

VINL

V

SSA1

V

DDA1

VOUTR

RTCB

GP4/BCKO

SHTCB

D−

7, 5, 3, 64,

62, 60, 58, 56

P0.7 to P0.0

14, 16, 18, 20,

22, 23, 29, 30

P2.0 to P2.7

D+

V

DDI

V

SSI

V

DDE

GP1/DI

GP0/BCKI

V

DDA2

BCK

48

EA

50

ALE

WS

DA

31

PSEN

V

SSA3

XTAL2a

V

DDA3

VRP

GP2/DO

GP3/WSO

XTAL1a

SDA

V

SSX

XTAL1b

XTAL2b

CLK

V

DDX

V

SSO

VOUTL

TC

SCL

V

DDO

V

SSE

GP5/WSI

The pin numbers given in parenthesis refer to the SDIP42 version.