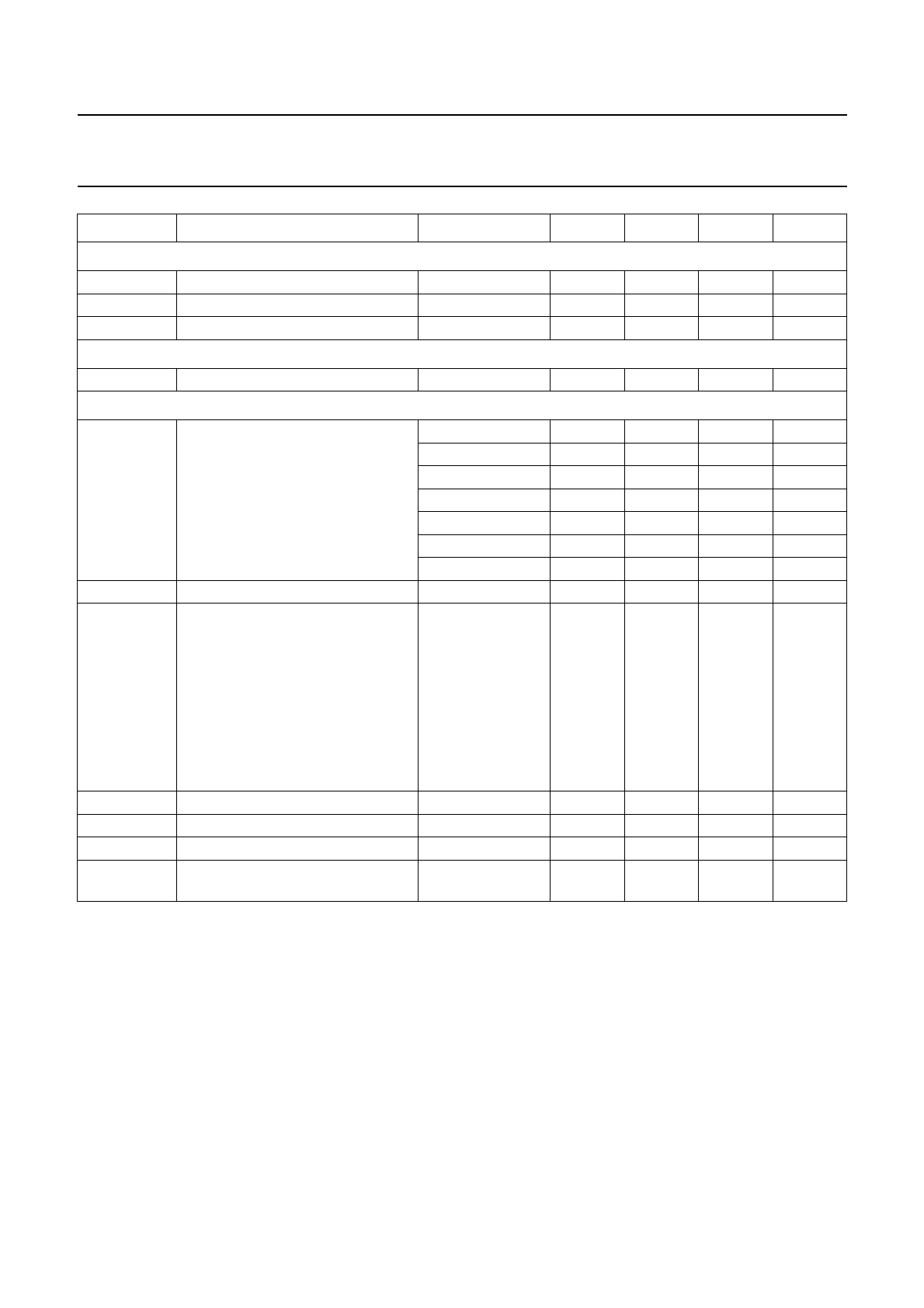

1999 May 10 42

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) CODEC UDA1325

Analog PLL (for ADC clock)

f

clk(PLL)

PLL clock frequency 8.1920 11.2896 12.2880 MHz

δ duty factor − 50 − %

t

strt(PO)

start-up time after power-on −−10 ms

Power-on reset

t

su(PO)

power-on set-up-time note 1 25C

ref

(2)

−−ms

PGA and ADC

V

i(FS)(rms)

full-scale input voltage (RMS value) PGA gain = −3dB − 1414

(3)

− mV

PGA gain=0dB − 1000 − mV

PGA gain=3dB − 708 − mV

PGA gain=9dB − 355 − mV

PGA gain = 15 dB − 178 − mV

PGA gain = 21 dB − 89 − mV

PGA gain = 27 dB − 44 − mV

C

i(PGA)

input capacitance of the PGA −−20 pF

(THD + N)/S total harmonic distortion plus

noise-to-signal ratio

f

s

= 44.1 kHz at

input signal of

1 kHz; PGA

gain = 0 dB;

note 4

V

i

(0 dB)

1.0 V (RMS)

−−85 −80 dB

− 0.0056 0.01 %

V

i

(−60 dB) −−30 −20 dB

− 3.2 10.0 %

S/N signal to noise ratio V

i

= 0.0 V 90 95 − dBA

α

ct

crosstalk between channels PGA gain=0dB − 100 − dB

f

s

sample frequency (128f

s

) 0.640 − 7.04 MHz

OL digital output level PGA gain=0dB,

V

i

= 1 V (RMS)

−−2.0 − dBFS

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT