APPLICATION

2.2 Interrupts

2-20

4513/4514 Group User’s Manual

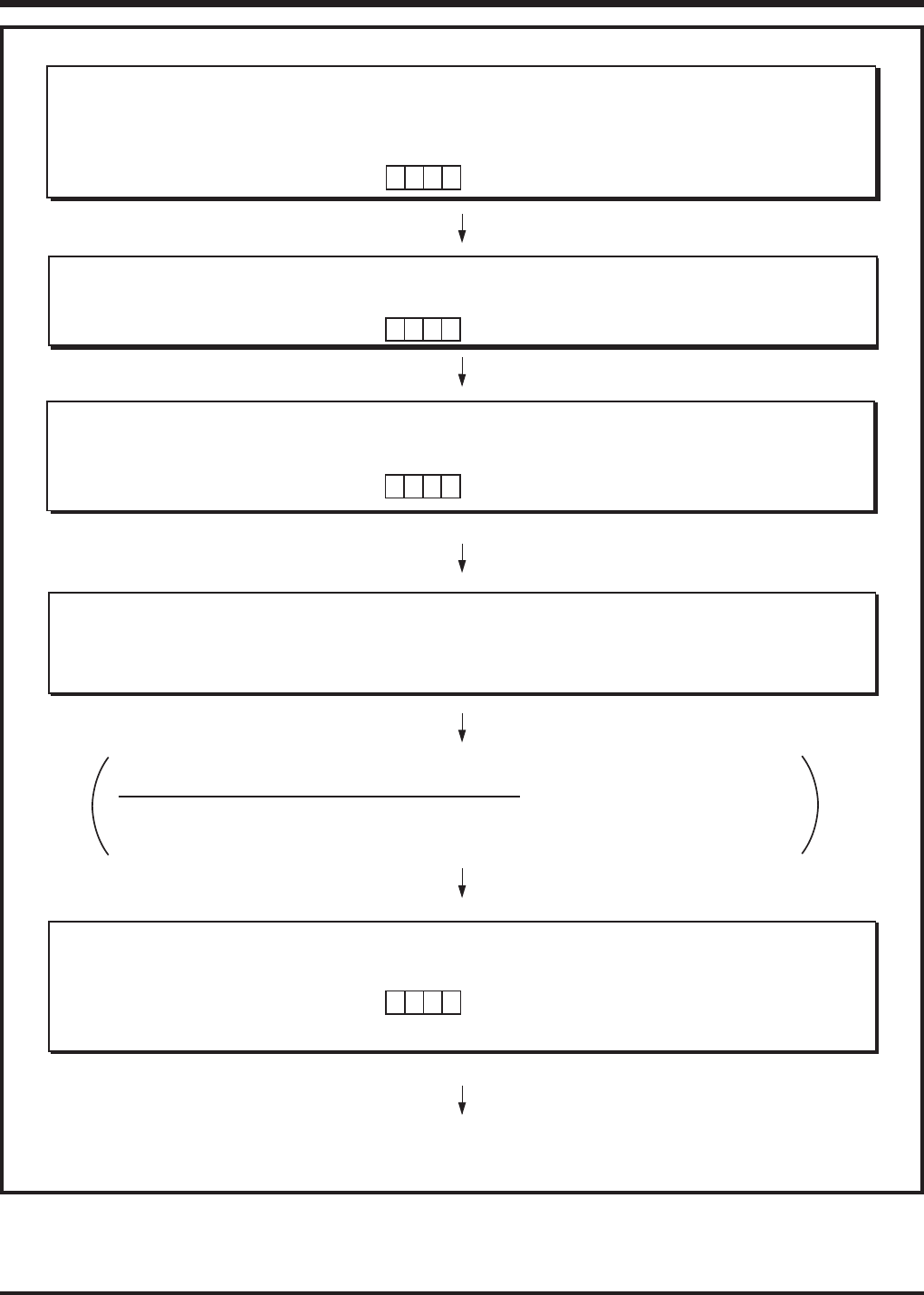

Fig. 2.2.4 INT1 interrupt setting example

Note: The valid waveforms causing the interrupt must be retained at their level for 4 cycles or more

of system clock.

➁ Set Port

Port used for INT1 interrupt is set to input port.

0

b3 b0

b3 b0

✕

1

✕✕

Both edges detection selected (TI2A instruction)

b3 b0

1

1

b3 b0

➀ Disable Interrupts

INT1 interrupt is temporarily disabled.

Interrupt enable flag INTE

Interrupt control register V1

“0”

✕✕ ✕

All interrupts disabled (DI instruction)

INT1 interrupt occurrence disabled

(TV1A instruction)

Port P31 output latch

✕✕ ✕

Set to input (OP3A instruction)

➂ Set Valid Waveform

Valid waveform of INT pin is selected.

Both edges detection selected

Interrupt control register I2

➃ Clear Interrupt Request

External interrupt activated condition is cleared.

INT1 interrupt request flag EXF1

“0”

INT1 interrupt activated condition cleared

(SNZ1 instruction)

Note when the interrupt request is cleared

When ➃ is executed, considering the skip of the next instruction according to the

interrupt request flag EXF1, insert the NOP instruction after the SNZ1 instruction.

➄ Enable Interrupts

The INT1 interrupt which is temporarily disabled is enabled.

Interrupt control register V1

Interrupt enable flag INTE

“1”

✕✕ ✕

INT1 interrupt occurrence enabled

(TV1A instruction)

All interrupts enabled (EI instruction)

INT1 interrupt execution started

“✕”: it can be “0” or “1.”