1-56

HARDWARE

4513/4514 Group User’s Manual

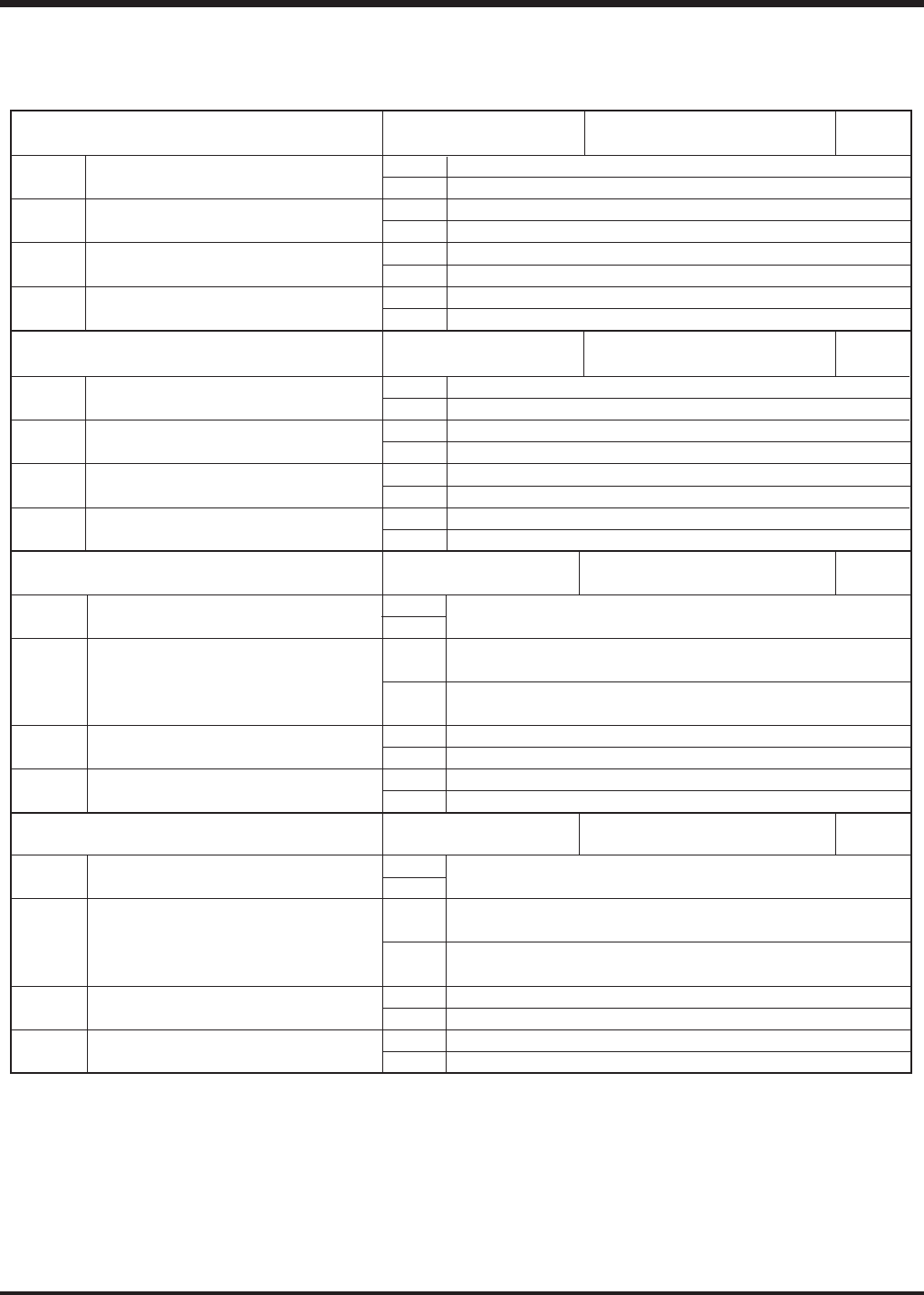

Table 22 Key-on wakeup control register, pull-up control register, and interrupt control register

K03

K02

K01

K00

Key-on wakeup control register K0

PU03

PU02

PU01

PU00

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Pins P12 and P13 key-on wakeup

control bit

Pins P10 and P11 key-on wakeup

control bit

Pins P02 and P03 key-on wakeup

control bit

Pins P00 and P01 key-on wakeup

control bit

at reset : 00002 at RAM back-up : state retained

0

1

0

1

0

1

0

1

Pull-up transistor OFF

Pull-up transistor ON

Pull-up transistor OFF

Pull-up transistor ON

Pull-up transistor OFF

Pull-up transistor ON

Pull-up transistor OFF

Pull-up transistor ON

Pins P12 and P13 pull-up transistor

control bit

Pins P10 and P11 pull-up transistor

control bit

Pins P02 and P03 pull-up transistor

control bit

Pins P00 and P01 pull-up transistor

control bit

R/W

Pull-up control register PU0 at reset : 00002 at RAM back-up : state retained

0

1

0

1

0

1

0

1

R/W

I13

I12

I11

I10

I23

I22

I21

I20

Not used

Interrupt valid waveform for INT0 pin/

return level selection bit (Note 2)

INT0 pin edge detection circuit control bit

INT0 pin

timer 1 control enable bit

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT1 pin is recognized with the SNZI1

instruction)/“L” level

Rising waveform (“H” level of INT1 pin is recognized with the SNZI1

instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

Not used

Interrupt valid waveform for INT1 pin/

return level selection bit (Note 3)

INT1 pin edge detection circuit control bit

INT1 pin

timer 3 control enable bit

Notes 1: “R” represents read enabled, and “W” represents write enabled.

2: When the contents of I1

2 is changed, the external interrupt request flag EXF0 may be set. Accordingly, clear EXF0 flag with the SNZ0 instruction.

3: When the contents of I2

2 is changed, the external interrupt request flag EXF1 may be set. Accordingly, clear EXF1 flag with the SNZ1 instruction.

Interrupt control register I1 R/Wat RAM back-up : state retainedat reset : 00002

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT0 pin is recognized with the SNZI0

instruction)/“L” level

Rising waveform (“H” level of INT0 pin is recognized with the SNZI0

instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Interrupt control register I2 R/Wat RAM back-up : state retainedat reset : 00002

FUNCTION BLOCK OPERATIONS