1-10

HARDWARE

4513/4514 Group User’s Manual

Notes 1: Pins except above have just single function.

2: The input of D

6, D7, P20–P22, CMP0-, CMP0+, CMP1-, CMP1+ and the input/output of P30, P31, P40–P43 can be used even when CNTR0, CNTR1,

S

CK, SOUT, SIN, INT0, INT1, and AIN0–AIN7 are selected.

3: The 4513 Group does not have P4

0/AIN4–P43/AIN7.

Notes 1: After system is released from reset, port P5 is in an input mode (di-

rection register FR0 = 0000

2)

2: When the P0

0–P03 and P10–P13 are connected to VSS, turn off

their pull-up transistors (register PU0i=“0”) and also invalidate the

key-on wakeup functions (register K0i=“0”) by software. When

these pins are connected to V

SS while the key-on wakeup func-

tions are left valid, the system fails to return from RAM back-up

state. When these pins are open, turn on their pull-up transistors

(register PU0i=“1”) by software, or set the output latch to “0.”

Be sure to select the key-on wakeup functions and the pull-up

functions with every two pins. If only one of the two pins for the

key-on wakeup function is used, turn on their pull-up transistors by

software and also disconnect the other pin. (i = 0, 1, 2, or 3.)

(Note when the output latch is set to “0” and pins are open)

● After system is released from reset, port is in a high-impedance state un-

til it is set the output latch to “0” by software. Accordingly, the voltage

level of pins is undefined and the excess of the supply current may occur

while the port is in a high-impedance state.

● To set the output latch periodically by software is recommended because

value of output latch may change by noise or a program run away

(caused by noise).

(Note when connecting to V

SS and VDD)

● Connect the unused pins to V

SS and VDD using the thickest wire at the

shortest distance against noise.

Pin

D6

D7

P20

P21

P22

P30

P31

Multifunction

CNTR0

CNTR1

SCK

SOUT

SIN

INT0

INT1

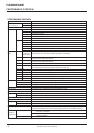

MULTIFUNCTION

Multifunction

CMP0-

CMP0+

CMP1-

CMP1+

AIN4

AIN5

AIN6

AIN7

Pin

AIN0

AIN1

AIN2

AIN3

P40

P41

P42

P43

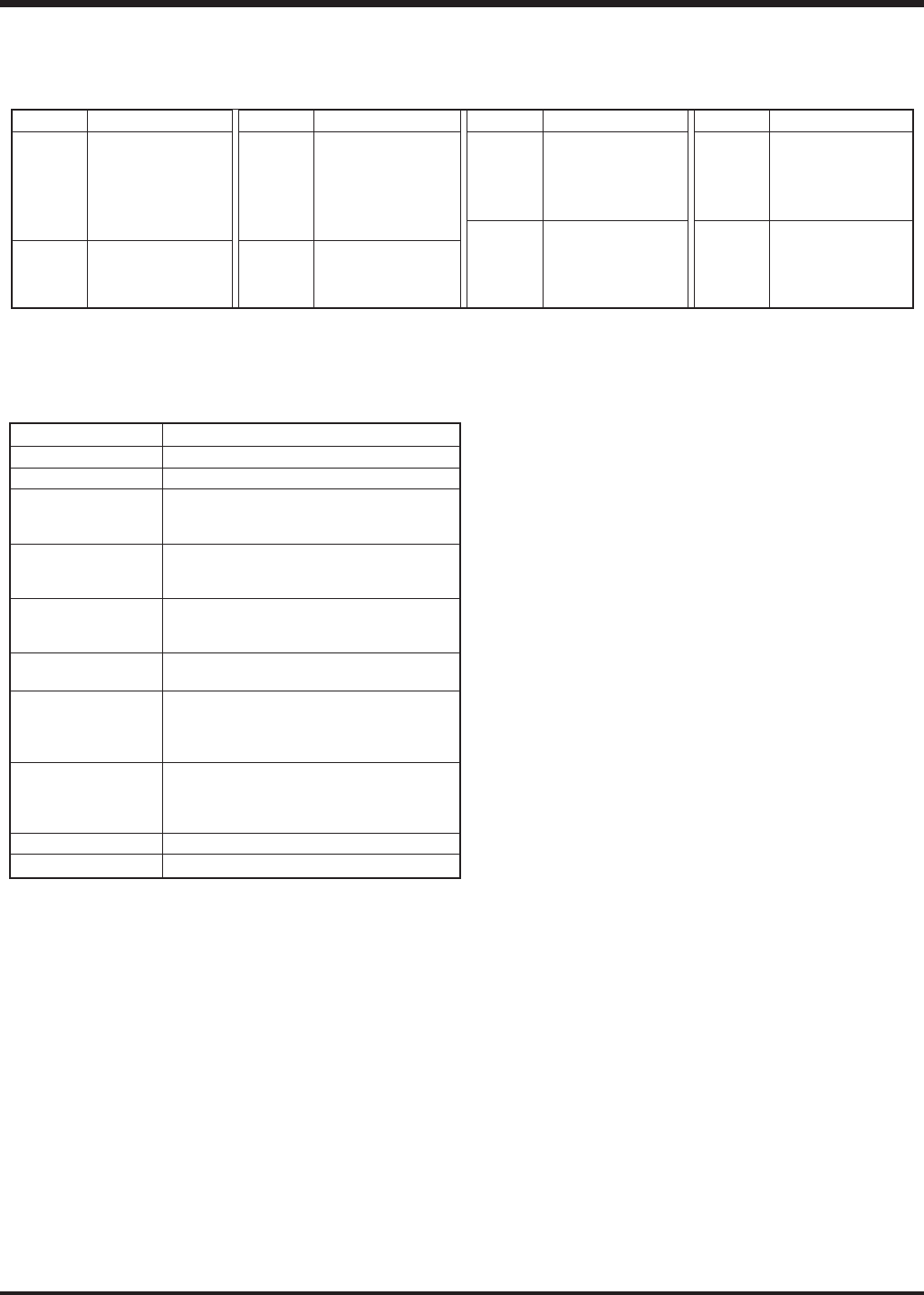

CONNECTIONS OF UNUSED PINS

Connection

Open (when using an external clock).

Connect to VSS.

Connect to VSS, or set the output latch to

“0” and open.

Connect to VSS.

Connect to VSS, or set the output latch to

“0” and open.

Connect to VSS, or set the output latch to

“0” and open.

When the input mode is selected by soft-

ware, pull-up to VDD through a resistor or

pull-down to VDD.

When selecting the output mode, open.

Connect to VSS.

Open or connect to VSS (Note 2)

Open or connect to VSS (Note 2)

Pin

XOUT

VDCE

D0–D5

D6/CNTR0

D7/CNTR1

P20/SCK

P21/SOUT

P22/SIN

P30/INT0

P31/INT1

P32, P33

P40/AIN4–P43/AIN7

P50–P53 (Note 1)

AIN0/CMP0-

AIN1/CMP0+

AIN2/CMP1-

AIN3/CMP1+

P00–P03

P10–P13

Pin

CNTR0

CNTR1

SCK

SOUT

SIN

INT0

INT1

Multifunction

D6

D7

P20

P21

P22

P30

P31

Multifunction

AIN0

AIN1

AIN2

AIN3

P40

P41

P42

P43

Pin

CMP0-

CMP0+

CMP1-

CMP1+

AIN4

AIN5

AIN6

AIN7

PIN DESCRIPTION