1

3

5

7

9

11

13

2

4

6

8

10

12

14

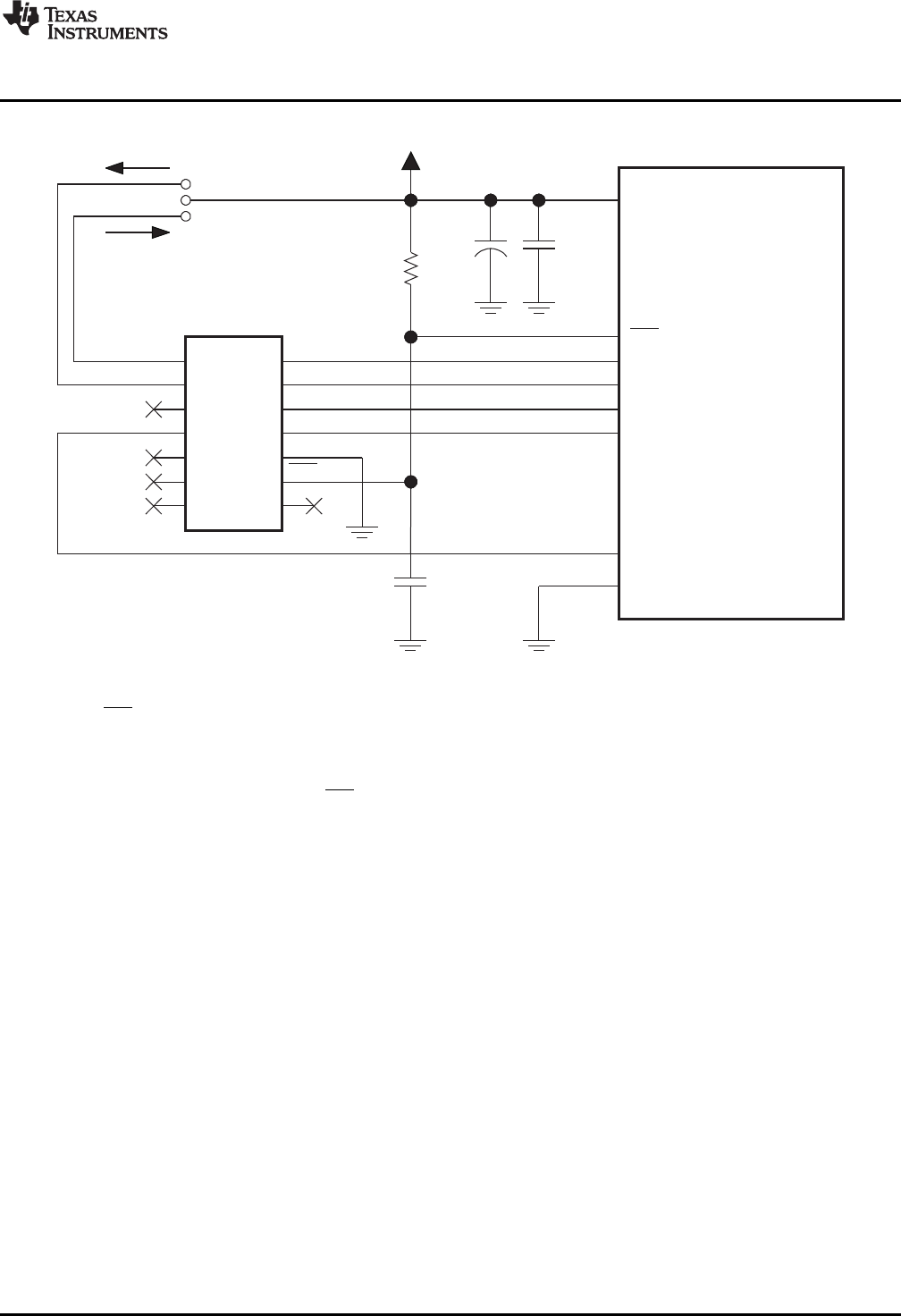

TDO/TDI

TDI/VPP

TMS

TCK

GND

TEST/VPP

JTAG

VCC TOOL

VCC TARGET

J1 (see Note A)

J2 (see Note A)

V

CC

R1

47 k

(see Note B)

W

C2

10 µF

C3

0.1 µF

V /AV /DV

CCCC CC

RST/NMI

TDO/TDI

TDI/VPP

TMS

TCK

TEST/VPP (see Note C)

V /AV /DV

SS SS SS

MSP430Fxxx

C1

10 nF/2.2 nF

(see Notes B and E)

RST (see Note D)

www.ti.com

Signal Connections for In-System Programming and Debugging

A Make either connection J1 in case a local target power supply is used or connection J2 to power target from the

debug/programming adapter.

B The RST/NMI pin R1/C1 configuration is device family dependent. See the respective MSP430 family user's guide for

the recommended configuration.

C The TEST pin is available only on MSP430 family members with multiplexed JTAG pins. See the device-specific data

sheet to determine if this pin is available.

D The connection to the JTAG connector RST pin is optional when using 4-wire JTAG communication mode

capable-only devices and not required for device programming or debugging. However, this connection is required

when using 2-wire JTAG communication mode capable devices in 4-wire JTAG mode.

E When using 2-wire JTAG communication capable devices in 4-wire JTAG mode, the upper limit for C1 should not

exceed 2.2 nF. This applies to both TI FET interface modules (LPT/USB FET).

Figure 2-1. Signal Connections for 4-Wire JTAG Communication

25

SLAU278F–May 2009–Revised December 2010 Design Considerations for In-Circuit Programming

Submit Documentation Feedback

© 2009–2010, Texas Instruments Incorporated