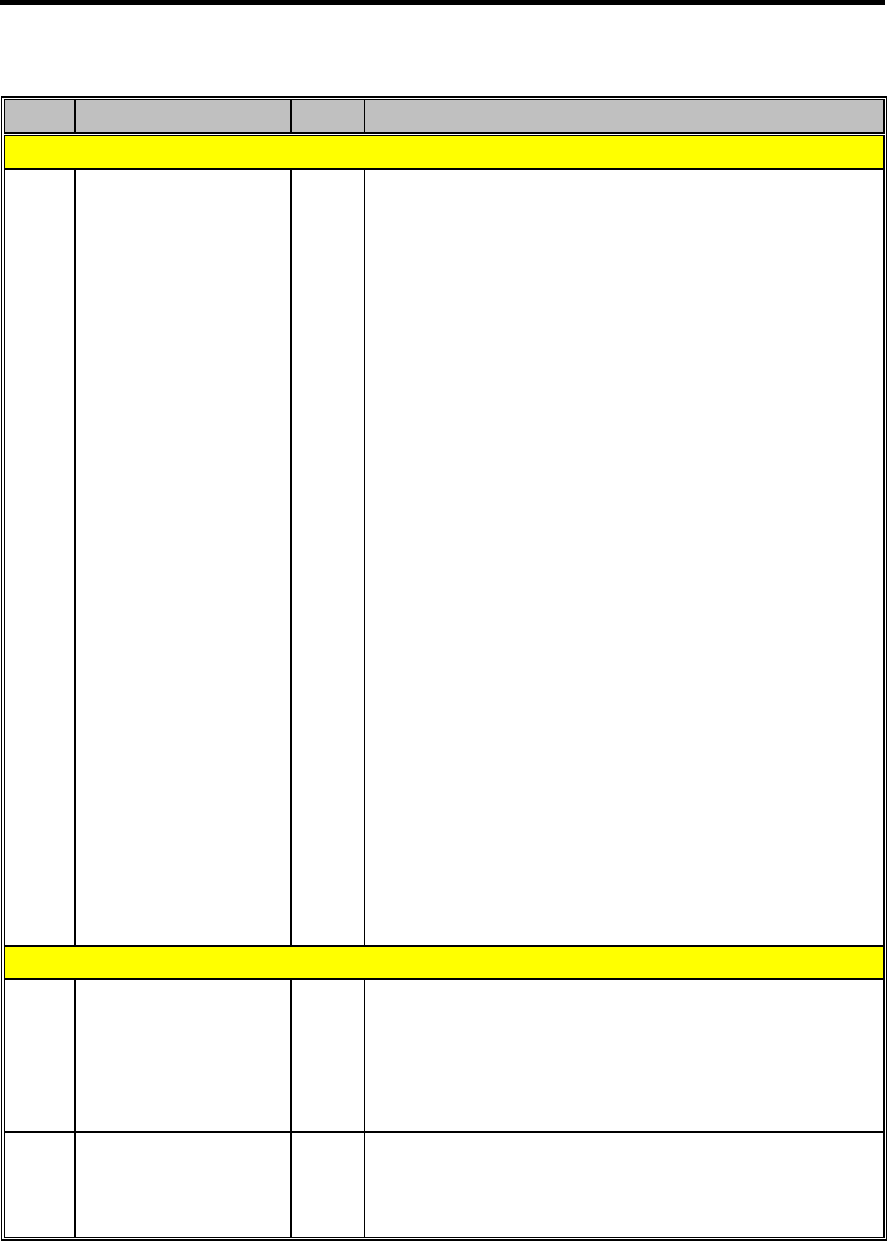

Major Chips Description 2-45

Table 2-10 C&T 65550 Pin Descriptions (continued)

Pin# Pin Name Type Description

CPU Direct / VL-Bus Interface (continued)

51

50

49

48

47

46

45

44

41

40

38

37

36

35

34

33

20

19

18

17

16

15

14

13

8

7

6

5

4

3

2

1

D00

D01

D02

D03

D04

D05

D06

D07

D08

D09

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

System Data Bus. In 32-bit CPU Local Bus designs these

data lines connect directly to the processor data lines. On

the VL-Bus they connect to the corresponding buffered or

unbuffered data signal. These pins are tri-stated during

Standby mode (as are all other bus interface outputs).

PCI Bus Interface

207 RESET# In Reset. This input sets all signals and registers in the chip to

a known state. All outputs from the chip are tri-stated or

driven to an inactive state. This pin is ignored during

Standby mode (STNDBY# pin low). The remainder of the

system (therefore the system bus) may be powered down if

desired (all bus output pins are tri-stated in Standby mode).

201 CLK In Bus Clock. This input provides the timing reference for all

bus transactions. All bus inputs except RESET# and INTA#

are sampled on the rising edge of CLK. CLK may be any

frequency from DC to 33MHz.