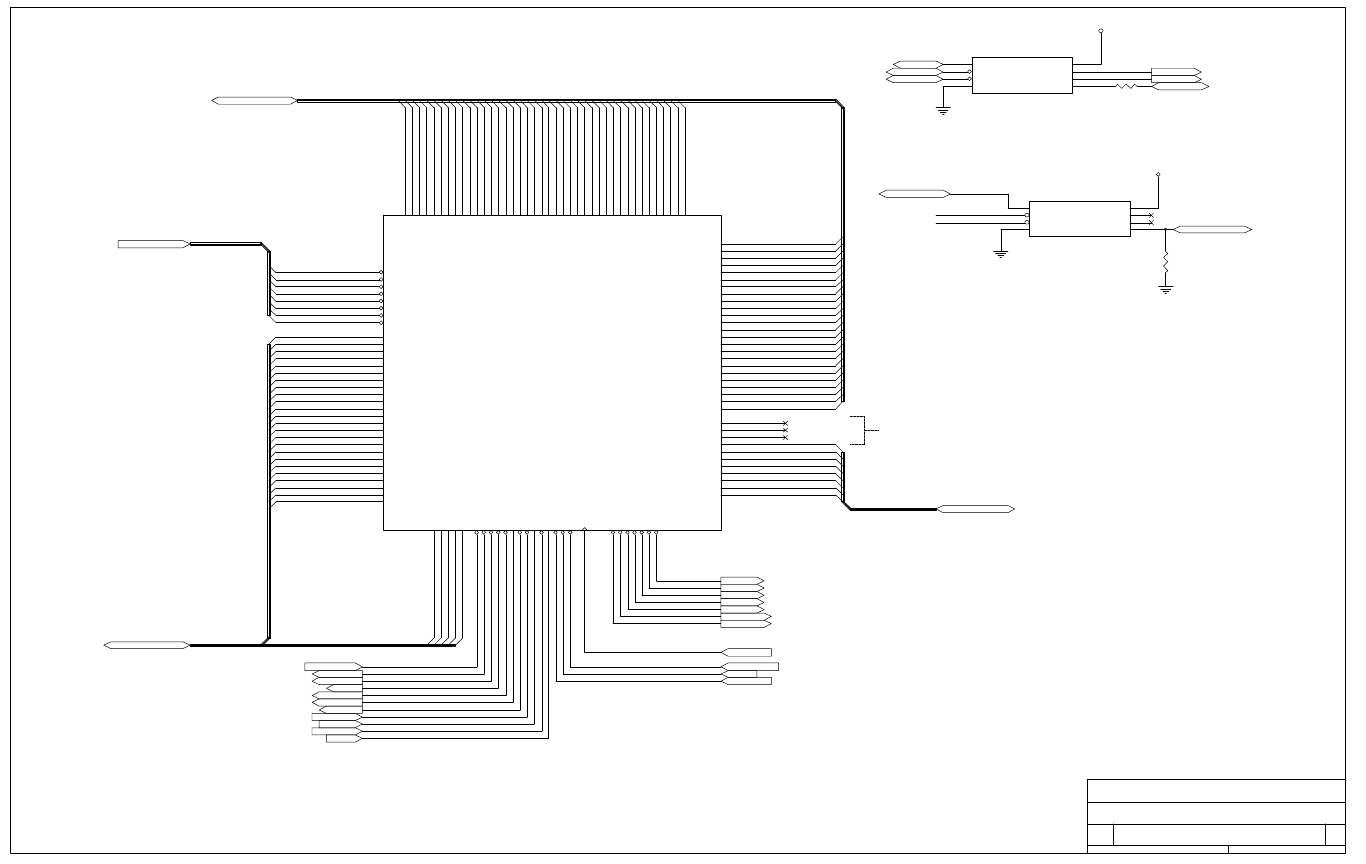

Date: February 12, 1997 Sheet 2 of 25

Size Document Number REV

A3 96149 SC

Title

370P/J (M1521 CPU TO PCI BRIDGE)

TAIPEI TAIWAN R.O.C

ACER

1 2

R103

33R3

DQ

1

CLK/CONV#

2

RST#

3

GND

4

VDD

8

THIGH

7

TLOW

6

TCOM

5

U18

DS1620

TH_COM

CPU_TH

CPU_TL

+5V

+5V

8,13

20

DQ

1

CLK/CONV#

2

RST#

3

GND

4

VDD

8

THIGH

7

TLOW

6

TCOM

5

U22

DS1620

TH_CLK

TH_RST#

TH_DQ

TH_DQ_VGA

$

C

P

U

D

2

5

$

C

P

U

D

2

4

TH_CLK

8

8

8

8

H

D

6

3

1

H

D

6

2

2

1

H

D

6

1

4

3

H

D

6

0

4

2

H

D

5

9

4

1

H

D

5

8

6

2

H

D

5

7

6

3

H

D

5

6

8

3

H

D

5

5

6

1

H

D

5

4

8

2

H

D

5

3

8

4

H

D

5

2

8

1

H

D

5

1

1

0

3

H

D

5

0

1

0

4

H

D

4

9

1

1

6

H

D

4

8

1

0

1

H

D

4

7

1

0

2

H

D

4

6

1

2

7

H

D

4

5

1

1

4

H

D

4

4

1

2

8

H

D

4

3

1

1

7

H

D

4

2

1

3

7

H

D

4

1

1

1

5

H

D

4

0

1

2

6

H

D

3

9

1

2

5

H

D

3

8

1

3

8

H

D

3

7

1

3

5

H

D

3

6

1

3

6

H

D

3

5

1

6

8

H

D

3

4

1

4

5

H

D

3

3

1

6

6

H

D

3

2

1

6

7

H

D

3

1

1

7

8

H

D

3

0

1

7

6

H

D

2

9

1

7

7

H

D

2

8

1

8

8

H

D

2

7

1

7

5

H

D

2

6

1

8

6

H

D

2

5

1

8

7

H

D

2

4

1

9

9

HD23

185

HD22

210

HD21

197

HD20

212

HD19

198

HD18

230

HD17

211

HD16

232

HD15

250

HD14

231

HD13

252

HD12

209

HD11

272

HD10

251

HD9

271

HD8

229

HD7

196

HD6

249

HD5

270

HD4

269

HD3

292

HD2

290

HD1

291

HD0

289

HBEJ0

146

HBEJ1

147

HBEJ2

148

HBEJ3

155

HBEJ4

156

HBEJ5

157

HBEJ6

158

HBEJ7

165

HA3

259

HA4

299

HA5

236

HA6

300

HA7

296

HA8

256

HA9

255

HA10

295

HA11

275

HA12

235

HA13

294

HA14

254

HA15

274

HA16

234

HA17

293

HA18

273

HA19

253

HA20

233

HA21

257

HA22

238

HA23

237

HA24

278

HA25

277

HA26

258

H

A

2

7

2

9

7

H

A

2

8

2

9

8

H

A

2

9

2

3

9

H

A

3

0

2

7

9

H

A

3

1

2

7

6

H

A

D

S

J

2

1

3

E

A

D

S

J

2

0

0

B

O

F

F

J

1

8

9

N

A

J

1

7

9

B

R

D

Y

J

1

6

9

A

H

O

L

D

1

5

9

K

E

N

J

/

I

N

V

1

4

9

C

A

C

H

E

J

1

3

9

M

I

O

J

1

2

9

H

L

O

C

K

J

1

1

8

D

C

J

2

1

5

H

I

T

M

J

2

1

6

W

R

J

2

1

7

S

M

I

A

C

T

J

2

1

8

TIO10/MWEJ1

308

TIO9/SRASJ1

307

TIO8/SCASJ1

287

TIO7

306

TIO6

286

TIO5

266

TIO4

222

TIO3

265

TIO2

245

TIO1

244

TIO0

191

C

A

D

V

J

/

C

A

A

4

J

2

6

3

C

A

D

S

J

/

C

A

A

3

J

2

8

3

C

C

S

J

2

8

4

G

W

E

J

3

0

4

C

O

E

J

2

4

3

B

W

E

J

/

C

G

C

S

J

3

0

5

T

W

E

J

2

6

4

H

C

L

K

I

N

1

5

0

U48

1521-27/A

$

C

P

U

D

6

3

$

C

P

U

D

6

2

$

C

P

U

D

6

1

$

C

P

U

D

6

0

$

C

P

U

D

5

9

$

C

P

U

D

5

8

$

C

P

U

D

5

7

$

C

P

U

D

5

6

$

C

P

U

D

5

5

$

C

P

U

D

5

4

$

C

P

U

D

5

3

$

C

P

U

D

5

2

$

C

P

U

D

5

1

$

C

P

U

D

5

0

$

C

P

U

D

4

9

$

C

P

U

D

4

8

$

C

P

U

D

4

7

$

C

P

U

D

4

6

$

C

P

U

D

4

5

$

C

P

U

D

4

4

$

C

P

U

D

4

3

$

C

P

U

D

4

2

$

C

P

U

D

4

1

$

C

P

U

D

4

0

$

C

P

U

D

3

9

$

C

P

U

D

3

8

$

C

P

U

D

3

7

$

C

P

U

D

3

6

$

C

P

U

D

3

5

$

C

P

U

D

3

4

$

C

P

U

D

3

3

$

C

P

U

D

3

2

$

C

P

U

D

3

1

$

C

P

U

D

3

0

$

C

P

U

D

2

9

$

C

P

U

D

2

8

$

C

P

U

D

2

7

$

C

P

U

D

2

6

$CPUD[0..63]

$CPUD[0..63]

1,5

$BE#[0..7]

$BE#[0..7]

$CPUA3

$CPUA4

$CPUA5

$CPUA6

$CPUA7

$CPUA8

$CPUA9

$CPUA10

$CPUA11

$CPUA12

$CPUA13

$CPUA14

$CPUA15

$BE#0

$BE#1

$BE#2

$BE#3

$BE#4

$BE#5

$BE#6

$BE#7

1

ALADDIN3

CPU BUS & CACHE

M1521

$TAG10

$CPUD23

$CPUD0

$CPUD1

$CPUD2

$CPUD3

$CPUD4

$CPUD5

$CPUD6

$CPUD7

$CPUD8

$CPUD9

$CPUD10

$CPUD11

$CPUD12

$CPUD13

$CPUD14

$CPUD15

$CPUD16

$CPUD17

$CPUD18

$CPUD19

$CPUD20

$CPUD21

$CPUD22

TH_RST#

1

2

R97

100KR3

TH_COM_VGA

13

5

FOR CACHE & SDRAM

NOT AVAILABLE IN II$TAG8

$TAG9

$TWE#

$BWE#

$COE#

$GWE#

$CCS#

$CADV#

$TAG[0..7]

$CADS#

$TAG0

$TAG1

$TAG2

$TAG3

$TAG4

$TAG5

$TAG6

$TAG7

$TAG[0..7]

5

5

5

5

5

5

5

$

C

P

U

A

2

7

$

C

P

U

A

2

8

$

C

P

U

A

2

9

$

C

P

U

A

3

0

$

C

P

U

A

3

1

$CPUA16

$CPUA17

$CPUA18

$CPUA19

$CPUA20

$CPUA21

$CPUA22

$CPUA23

$CPUA24

$CPUA25

$CPUA26

$BRDY#

$KEN#

$DC#

$MIO#

$CACHE#

$CPUA[3..31]

$EADS#

$BOFF#

$NA#

$AHOLD

$HLOCK#

$CPUADS#

$CPUA[3..31]

1

1

1

1

1,8

1,5

1

1

1

1

1

1

$BRDY#

$KEN#

$MIO#

$CACHE#

$EADS#

$BOFF#

$NA#

$AHOLD

$HLOCK#

$DC#

$CPUADS#

$WR#

$HITM#

$SMIACT#

$21CLK

$WR#

$HITM#

$SMIACT#

$21CLK

1

1

1

7