2-52 Service Guide

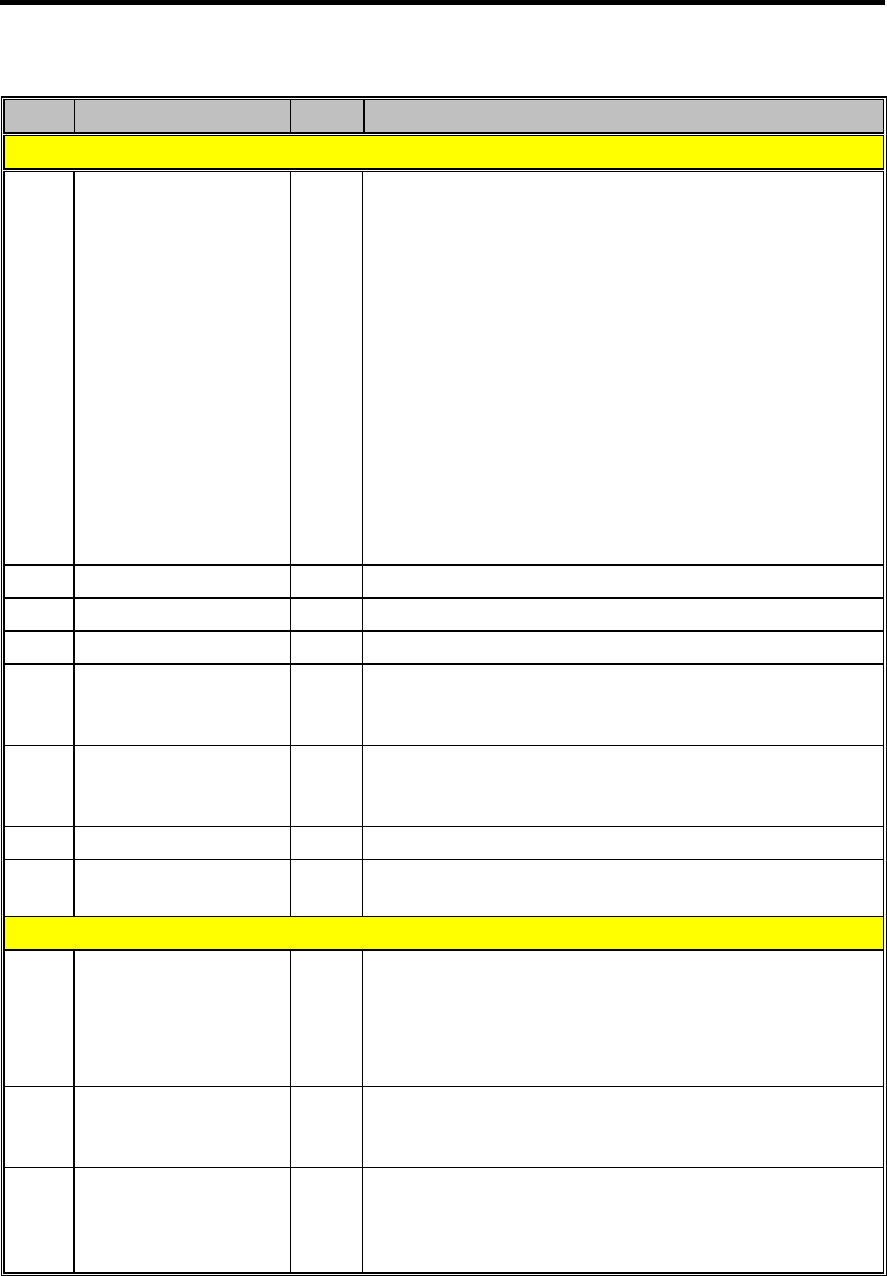

Table 2-10 C&T 65550 Pin Descriptions (continued)

Pin# Pin Name Type Description

Flat Panel Display Interface

71

72

73

74

75

76

78

79

81

82

83

84

85

86

87

88

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

8, 9, 12, or 16-bit flat panel data output. 18-bit and 24-bit

panel interfaces may also be supported (see CA0-7 for P16-

23).

Refer to Table 2-7 for the configurations for various panel

types.

70 SHFCLK Out Shift Clock. Pixel clock for flat panel data.

67 FLM Out First Line Marker. Flat Panel equivalent of VSYNC.

68 LP Out Latch Pulse. Flat Panel equivalent of HSYNC.

69 M (DE) (BLANK#) Out M signal for panel AC drive control. (may also be called

ACDCLK). May also be configured as BLANK# or as Display

Enable (DE) for TFT Panels.

62

61

ENAVDD

ENAVEE (ENABKL)

I/O

I/O

Power sequencing controls. Power sequencing controls. for

panel driver electronics voltage VDD and panel LCD bias

voltage VEE

53 ACTI I/O Activity Indicator. May be configured for other functions

54 ENBKL I/O Enable Backlight Outputs. May be configured for other

functions

Flat Panel Display Interface

65 HYSNC (CSYNC) Out CRT Horizontal Sync (polarity is programmable) or

"Composite Sync" for support of various external NTSC / PAL

encoder chips.

Note CSYNC can be set to output on the ACTI or ENABKL

pins.

64 VSYNC (VISINT) Out CRT Vertical Sync (polarity is programmable) or "Vsync

Interval" for support of various external NTSC / PAL encoder

chips.

60

58

57

RED

GREEN

BLUE

Out CRT analog video outputs from the internal color palette

DAC. The DAC is designed for a 37.5 Ω equivalent load on

each pin (e.g. 75 Ω resistor on the board, in parallel with the

75 Ω CRT load.