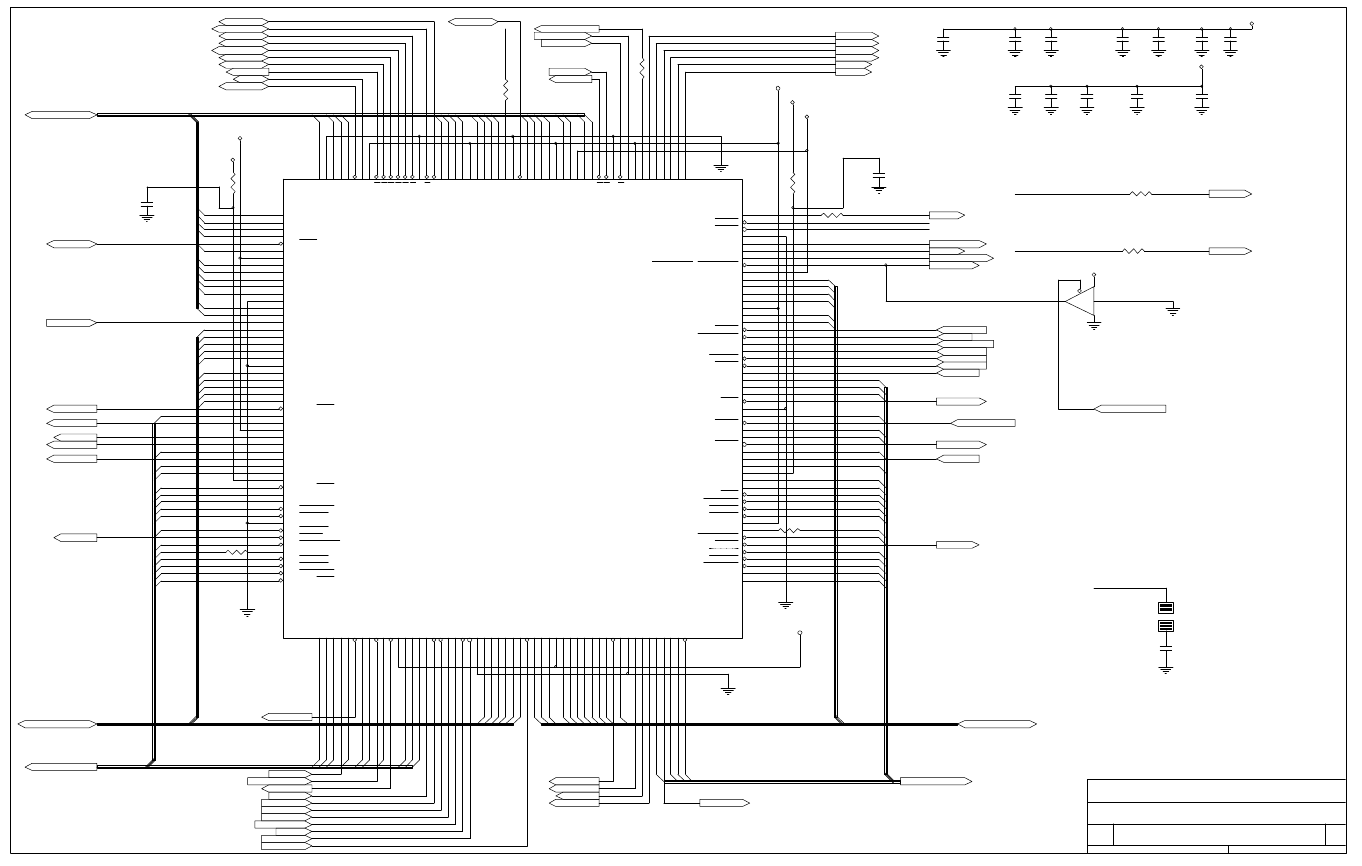

Date: February 12, 1997 Sheet 21 of 25

Size Document Number REV

A3 96149 SC

Title

370P/J (PCI1131 CARD BUS CONTROLLER)

TAIPEI TAIWAN R.O.C

ACER

C188

SCD1U

C202

SCD1U

C214

SCD1U

C209

SC10U16V

C190

SCD1U

C34

SCD1U

C35

SC10U16V

C37

SC1KP

C198

SC1KP

1 2

R151

0R3

INTD#

1130_INTB# INTD#

3.3V

3.3V

3,4

C187

SCD1U

1

2

R161

100R3

C73

SCD1U

C74

SC1KP

IRQ14

IRQ12

IRQ11

IRQ10

IRQ9

IRQ7

IRQ5

IRQ5

I

R

Q

9

I

R

Q

7

A_SLOT_VCC

3.3V

+5V

4

4

4

4

4,13

4

CX10

SCD1U

## ADD CX10,CX11

1 2

RX10

0R3

1

2

R185

0R3

1

2

R148

33R3

GNT#1

REQ#1

RING_OUT#

PCIRST#

CBE#3

$CARDCLK

A

D

1

5

P

A

R

S

E

R

R

#

P

E

R

R

#

S

T

O

P

#

D

E

V

S

E

L

#

T

R

D

Y

#

I

R

D

Y

#

F

R

A

M

E

# A

D

1

6

A

D

1

7

A

D

1

8

A

D

1

9

A

D

2

0

A

D

2

1

A

D

2

2

A

D

2

3

A

D

2

4

A

D

2

5

A

D

2

6

A

D

2

7

A

D

2

8

A

D

2

9

A

D

3

0

A

D

3

1

A

D

2

0

I

R

Q

1

4

I

R

Q

1

2

I

R

Q

1

1

I

R

Q

1

0

C

B

E

#

1

C

B

E

#

3

C

B

E

#

2

3,4,8,17,21

3

3

24

7

8

1

2

R164

100R3

AD[0..31]

FRAME#

IRDY#

DEVSEL#

STOP#

SERR#

PERR#

PAR

TRDY#

CBE#1

CBE#2

AD11

A

D

1

2

A

D

1

3

A

D

1

4

AD[0..31]

B_SLOT_VCC

3.3V

AD11

1

AD10

2

AD9

3

AD8

4

C/BE0

5

AD7

6

VCC

7

AD6

8

AD5

9

AD4

10

AD3

11

AD2

12

GND

13

AD1

14

AD0

15

B_CCD1

16

B_CAD0

17

B_CAD2

18

B_CAD1

19

B_CAD4

20

B_CAD3

21

GND

22

B_CAD6

23

B_CAD5

24

B_RSVD

25

B_CAD7

26

B_CAD8

27

B_CC/BE0

28

B_CAD9

29

B_CAD10

30

VCC

31

B_CAD11

32

B_CAD13

33

B_CAD12

34

B_CAD15

35

B_CAD14

36

B_CAD16

37

VCCARDBUS

38

B_CC/BE1

39

B_RSVD

40

B_CPAR

41

B_CBLOCK

42

B_CPERR

43

GND

44

B_CSTOP

45

B_CGNT

46

B_CDEVSEL

47

B_CCLK

48

B_CTRDY

49

B_CIRDY

50

B_CFRAME

51

B_CC/BE2

52

B

_

C

A

D

1

7

5

3

B

_

C

A

D

1

8

5

4

B

_

C

A

D

1

9

5

5

B

_

C

V

S

2

5

6

B

_

C

A

D

2

0

5

7

B

_

C

R

S

T

5

8

B

_

C

A

D

2

1

5

9

B

_

C

A

D

2

2

6

0

B

_

C

R

E

Q

6

1

B

_

C

A

D

2

3

6

2

B

_

C

C

/

B

E

3

6

3

V

C

C

6

4

B

_

C

A

D

2

4

6

5

B

_

C

A

D

2

5

6

6

B

_

C

A

D

2

6

6

7

B

_

C

V

S

1

6

8

B

_

C

I

N

T

6

9

B

_

C

S

E

R

R

7

0

B

_

C

A

U

D

I

O

7

1

B

_

C

S

T

S

C

H

G

7

2

B

_

C

C

L

K

R

U

N

7

3

B

_

C

C

D

2

7

4

G

N

D

7

5

B

_

C

A

D

2

7

7

6

B

_

C

A

D

2

8

7

7

B

_

C

A

D

2

9

7

8

B

_

C

A

D

3

0

7

9

B

_

R

S

V

D

8

0

B

_

C

A

D

3

1

8

1

A

_

C

C

D

1

8

2

A

_

C

A

D

0

8

3

A

_

C

A

D

2

8

4

A

_

C

A

D

1

8

5

V

C

C

8

6

A

_

C

A

D

4

8

7

A

_

C

A

D

3

8

8

A

_

C

A

D

6

8

9

A

_

C

A

D

5

9

0

A

_

R

S

V

D

9

1

A

_

C

A

D

7

9

2

A

_

C

A

D

8

9

3

A

_

C

C

/

B

E

O

9

4

A

_

C

A

D

9

9

5

G

N

D

9

6

A

_

C

A

D

1

0

9

7

A

_

C

A

D

1

1

9

8

A

_

C

A

D

1

3

9

9

A

_

C

A

D

1

2

1

0

0

A

_

C

A

D

1

5

1

0

1

A

_

C

A

D

1

4

1

0

2

A

_

C

A

D

1

6

1

0

3

A

_

C

C

/

B

E

1

1

0

4

A_RSVD

105

A_CPAR

106

A_CBLOCK

107

A_CPERR

108

A_CSTOP

109

A_CGNT

110

A_CDEVSEL

111

A_CCLK

112

VCC

113

A_CTRDY

114

A_CIRDY

115

A_CFRAME

116

A_CC/BE2

117

A_CAD17

118

A_CAD18

119

VCCA

120

A_CAD19

121

A_CVS2

122

A_CAD20

123

A_CRST

124

A_CAD21

125

A_CAD22

126

A_CREQ

127

A_CAD23

128

GND

129

A_CC/BE3

130

A_CAD24

131

A_CAD25

132

A_CAD26

133

A_CVS1

134

A_CINT

135

A_CSERR

136

A_CAUDIO

137

A_CSTSCHG

138

A_CCLKRUN

139

A_CCD2

140

A_CAD27

141

A_CAD28

142

VCC

143

A_CAD29

144

A_CAD30

145

A_RSVD

146

A_CAD31

147

VCCP

148

SPKROUT/SUSPEND

149

LATCH

150

CLOCK

151

DATA

152

GND

153

IRQ3/INTA

154

IRQ4/INTB

155

IRQ5

156

I

R

Q

7

1

5

7

I

R

Q

9

/

I

R

Q

S

E

R

1

5

8

I

R

Q

1

0

1

5

9

I

R

Q

1

1

1

6

0

I

R

Q

1

2

1

6

1

I

R

Q

1

4

1

6

2

I

R

Q

1

5

/

R

I

_

O

U

T

1

6

3

V

C

C

1

6

4

P

C

L

K

1

6

5

R

S

T

I

N

1

6

6

G

N

D

1

6

7

G

N

T

1

6

8

R

E

Q

1

6

9

A

D

3

1

1

7

0

A

D

3

0

1

7

1

V

C

C

P

1

7

2

A

D

2

9

1

7

3

A

D

2

8

1

7

4

V

C

C

1

7

5

A

D

2

7

1

7

6

A

D

2

6

1

7

7

A

D

2

5

1

7

8

A

D

2

4

1

7

9

C

/

B

E

3

1

8

0

G

N

D

1

8

1

I

D

S

E

L

1

8

2

A

D

2

3

1

8

3

A

D

2

2

1

8

4

A

D

2

1

1

8

5

A

D

2

0

1

8

6

V

C

C

1

8

7

A

D

1

9

1

8

8

A

D

1

8

1

8

9

A

D

1

7

1

9

0

A

D

1

6

1

9

1

C

/

B

E

2

1

9

2

F

R

A

M

E

1

9

3

G

N

D

1

9

4

I

R

D

Y

1

9

5

T

R

D

Y

1

9

6

D

E

V

S

E

L

1

9

7

S

T

O

P

1

9

8

P

E

R

R

1

9

9

S

E

R

R

2

0

0

V

C

C

2

0

1

P

A

R

2

0

2

C

/

B

E

1

2

0

3

A

D

1

5

2

0

4

A

D

1

4

2

0

5

A

D

1

3

2

0

6

G

N

D

2

0

7

A

D

1

2

2

0

8

U33

PCI1131

3,4,8,17,21

3,4,8,17,21

3,4,8,17

3,4,8,17

3,4,8,17

3,4,8,17

3,4,17

3,4,8,17

4

3,17

CX11

SCD1U

B_CD1#

B_CE1#

B_CE2#

CBE#0

AD8

AD9

AD10

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

B_CD1#

B_CE1#

B_A10

B_CE2#

B_D3

B_D11

B_D4

B_D12

B_D5

B_D13

B_D6

B_D14

B_D7

B_D15

CBE#0

22

22

22

A_CD2#

A_STSCG#

A_SPKR#

A_WP

A_INPACK#

A_WAIT#

A_REG#

SER_DATA

SCLK

SER_LATCH

A_IREQ#

PCMSPK

A_VS1

A_D10

A_D8

A_D2

A_D9

A_D1

A_D0

A_CD2#

A_WP

A_STSCG#

A_SPKR#

A_WAIT#

A_IREQ#

A_A0

A_A1

A_A2

A_REG#

A_A3

1130_INTB#

1130_INTA#

A_VS1

4

22

22

22

19,22

22

22

22

22

22

22

16

22

1 2

R152

0R3

INTA#

1130_INTA#

3,4

22

3.3V

INVAPMSEL0

12 11

1

4

1

3

7

U34D

SSLVC125

1

2

R149

DUMMY-R3

$CARDCLK

1 2

R160

33R3

A_RESET

A_WE#

A_VS2

A_A4

A_A5

A_RESET

A_A6

A_A25

A_A7

A_A24

A_A12

A_A23

A_A15

A_A22

A_A16

A_WE#

A_A20

A_A14

A_A19

A_A13

A_A18

A_A21

A_VS2

3.3V

22

22

22

1 2

R168

33R3

B_OE#

B_IORD#

B_IOWR#

B_WE#

B_IORD#

B_A11

B_IOWR#

B_OE#

B_A9

B_A17

B_A18

B_A13

B_A19

B_A14

B_A20

B_WE#

B_A21

B_A22

B_A15

B_A23

B_A12

B_A16

B_A8

22

22

22

22

B_D[0..15]

B_A[0..25]

B_REG#

B_WAIT#

B_SPKR#

B_STSCG#

B_WP

B_CD2#

A_CD1#

B_INPACK#

B_RESET

B_IREQ#

B_VS1

B_VS2

B

_

A

2

4

B

_

A

7

B

_

A

2

5

22

22

22

22

22

22

22

22

22

22

22

22

22

A_OE#

A_IORD#

A_CE1#

A_CE2#

B

_

A

6

B

_

A

5

B

_

A

4

B

_

A

3

B

_

R

E

G

#

B

_

A

2

B

_

A

1

B

_

A

0

B

_

I

R

E

Q

#

B

_

W

A

I

T

#

B

_

S

P

K

R

#

B

_

S

T

S

C

G

#

B

_

W

P

B

_

C

D

2

#

B

_

D

0

B

_

D

8

B

_

D

1

B

_

D

9

B

_

D

2

B

_

D

1

0

A

_

D

3

A

_

D

1

1

A

_

D

4

A

_

D

1

2

A

_

D

5

A

_

D

1

3

A

_

D

6

A

_

D

1

4

A

_

D

7

A

_

D

1

5

A

_

C

E

1

#

A

_

A

1

0

A

_

C

E

2

#

A

_

O

E

#

A

_

I

O

R

D

#

A

_

A

1

1

A

_

I

O

W

R

#

A

_

A

9

A

_

C

D

1

#

B

_

V

S

1

22

22

22

22

A_A[0..25]

A_D[0..15]

A_IOWR#

A

_

A

1

7

A

_

A

8

A_D[0..15]

15,19,22

22

C189

SC33P

22